Архитектура 32-битных процессоров IA-32. (Лекция 3) презентация

Содержание

- 2. Структура микропроцессора Intel 80386

- 3. Регистры ЦП 80386 Программно доступные регистры: 8 регистров общего

- 4. Режимы работы ЦП 80386 Реальный режим или режим реальных адресов.

- 5. ЦП 80386 (переключение режимов)

- 6. Формирование линейного адреса без участия селекторов В режиме

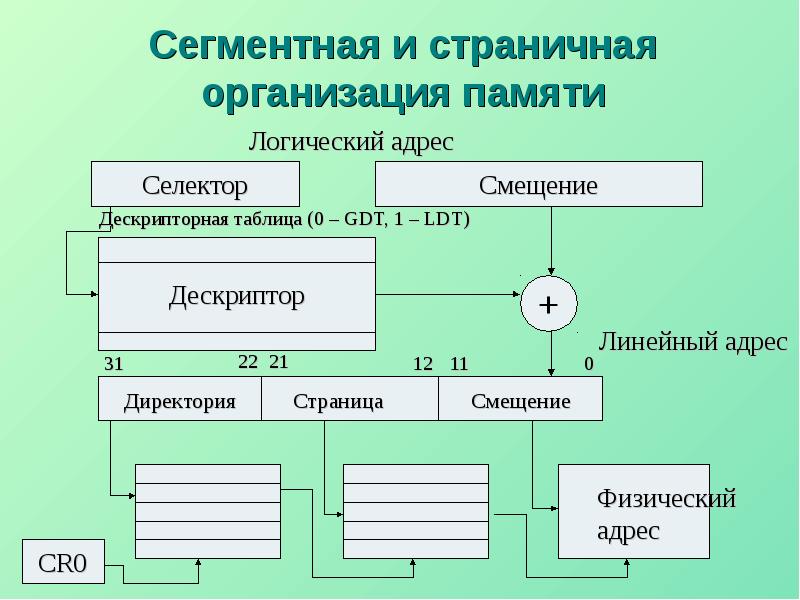

- 7. Формирование линейного адреса в защищенном режиме Если в

- 8. Сегментная и страничная организация памяти

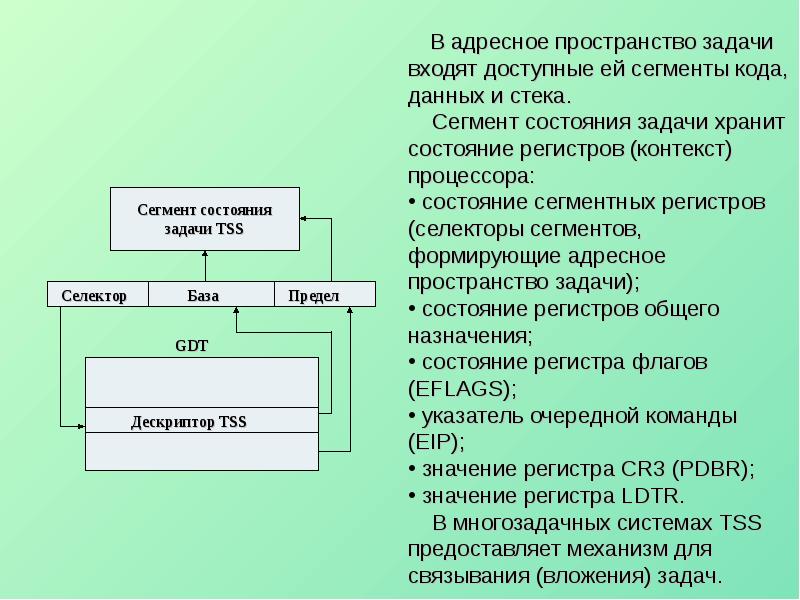

- 9. Многозадачность в ЦП 80386 Многозадачность - это метод управления

- 11. Сравнительные характеристики режимов работы процессора

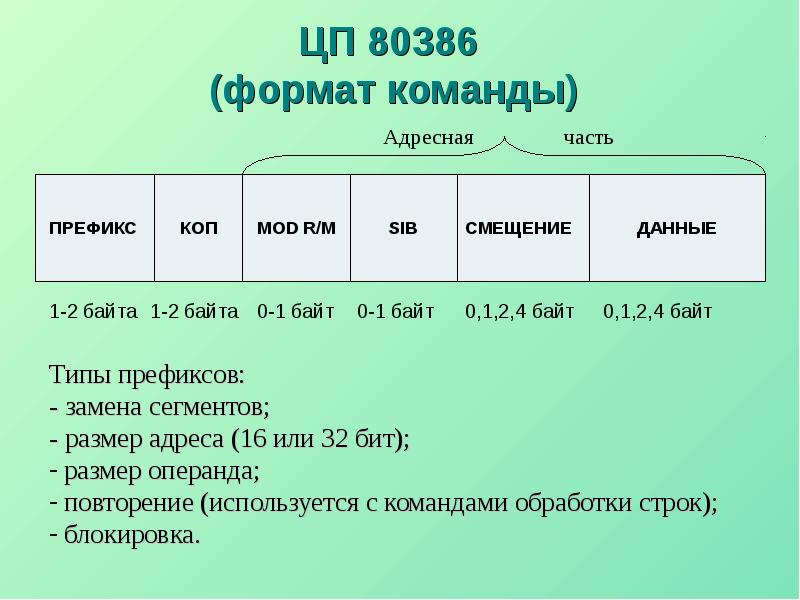

- 12. ЦП 80386 (формат команды)

- 13. Формат команды КОП - код операции. Байт "Mod R/M" определяет режим

- 14. Структура микропроцессора Intel 80486

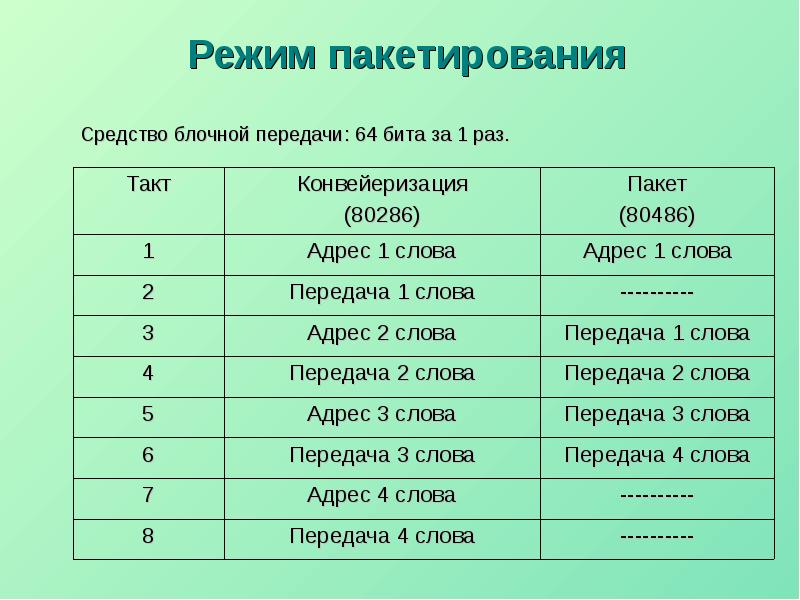

- 15. Режим пакетирования

- 16. Уровни привилегий в IA32 Архитектура защиты МП обеспечивает 4

- 17. ЦП 80486 (уровни привилегий)

- 18. Структуры с привилегиями CPL – текущий уровень привилегий (Current Privilege

- 19. Правила на основе привилегий

- 20. Вопросы для самоконтроля Какие регистры составляют программная модель ЦП 80386? В

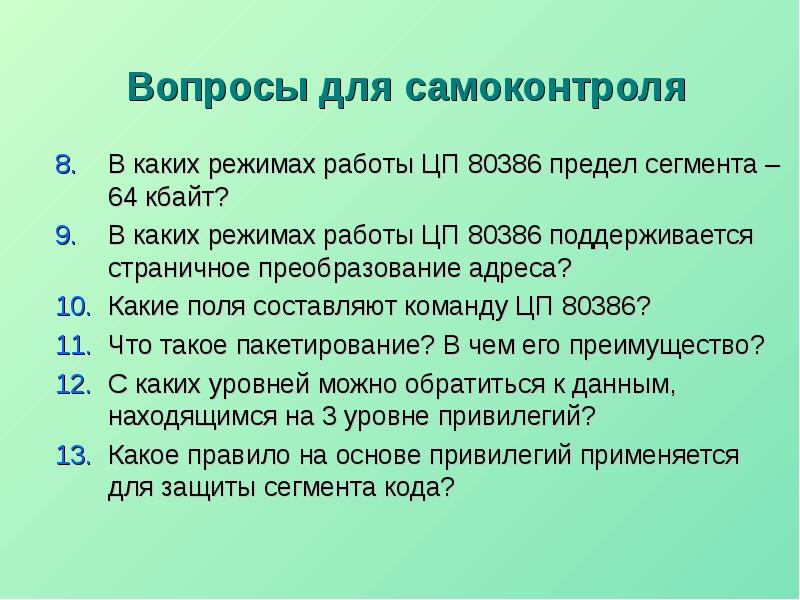

- 21. Вопросы для самоконтроля В каких режимах работы ЦП 80386 предел сегмента

- 22. Скачать презентацию

Слайды и текст этой презентации

Скачать презентацию на тему Архитектура 32-битных процессоров IA-32. (Лекция 3) можно ниже:

Похожие презентации