Архитектура вычислительных систем. Терминология, классификационные принципы презентация

Содержание

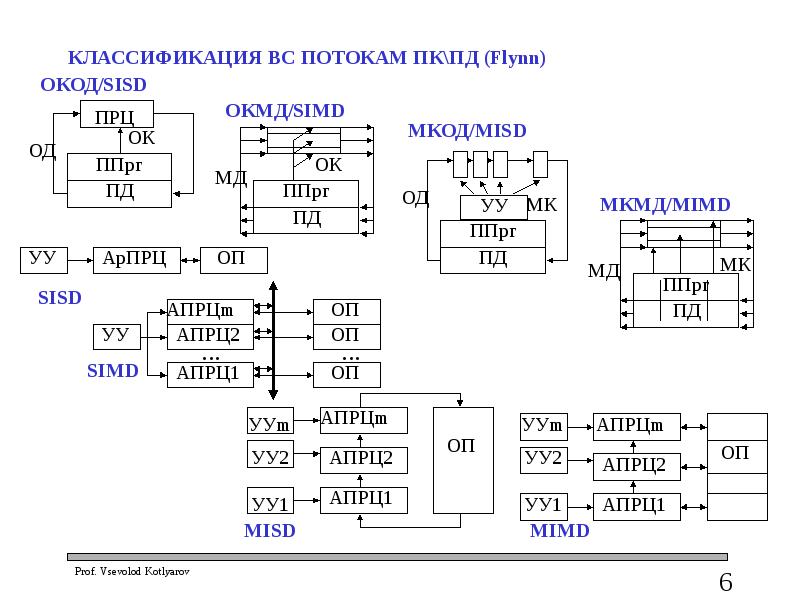

- 6. КЛАССИФИКАЦИЯ ВС ПОТОКАМ ПК\ПД (Flynn)

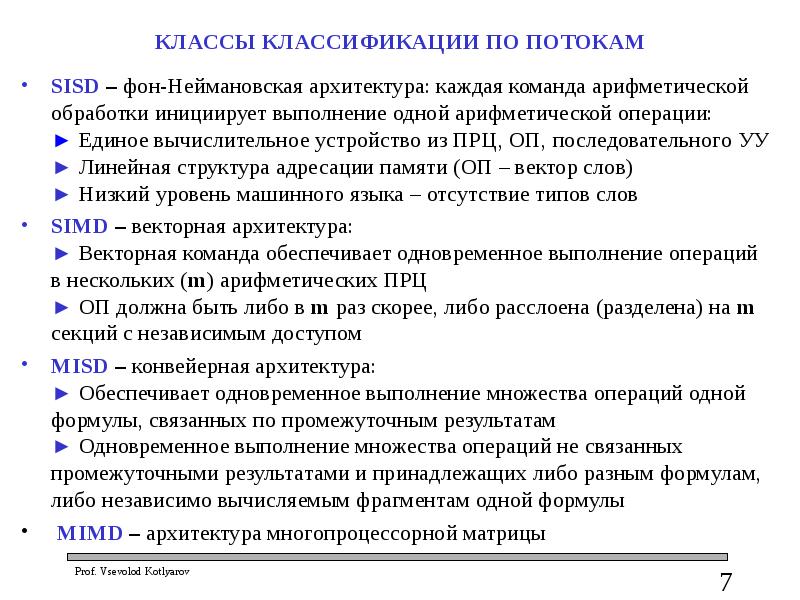

- 7. КЛАССЫ КЛАССИФИКАЦИИ ПО ПОТОКАМ SISD – фон-Неймановская архитектура: каждая команда арифметической

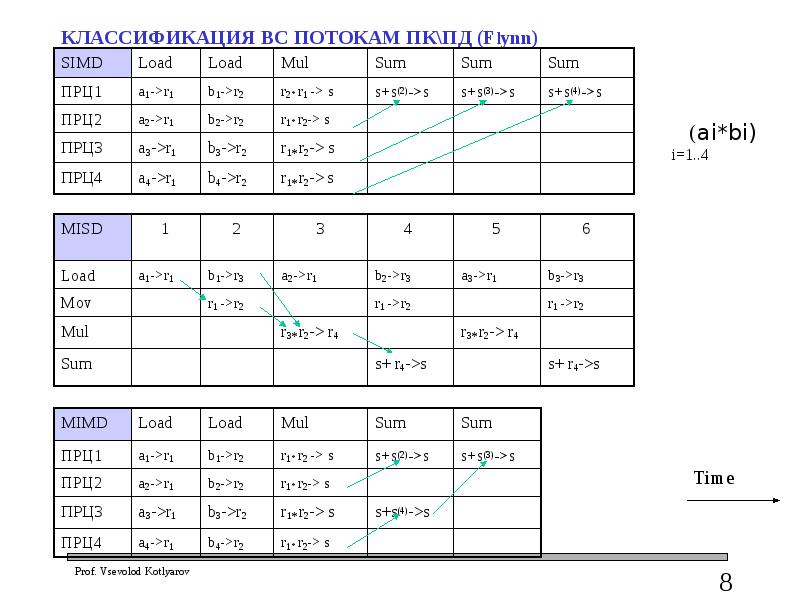

- 8. КЛАССИФИКАЦИЯ ВС ПОТОКАМ ПК\ПД (Flynn)

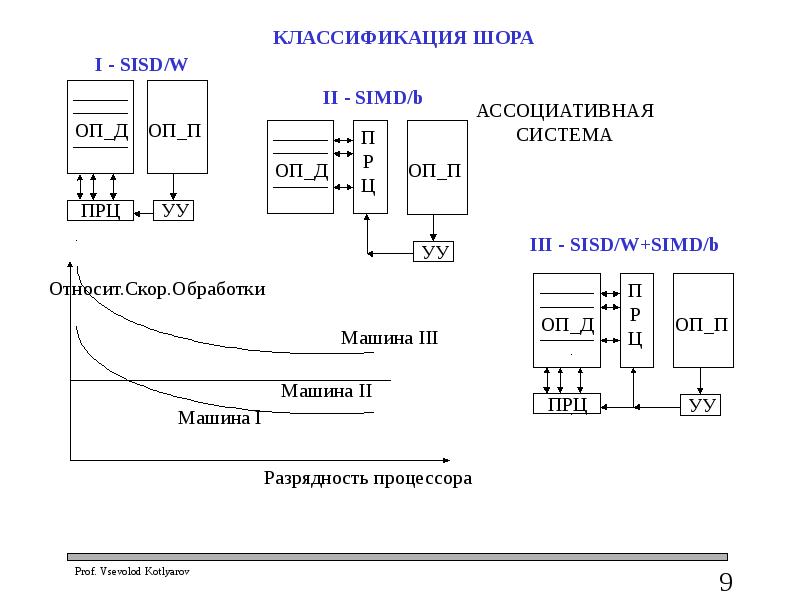

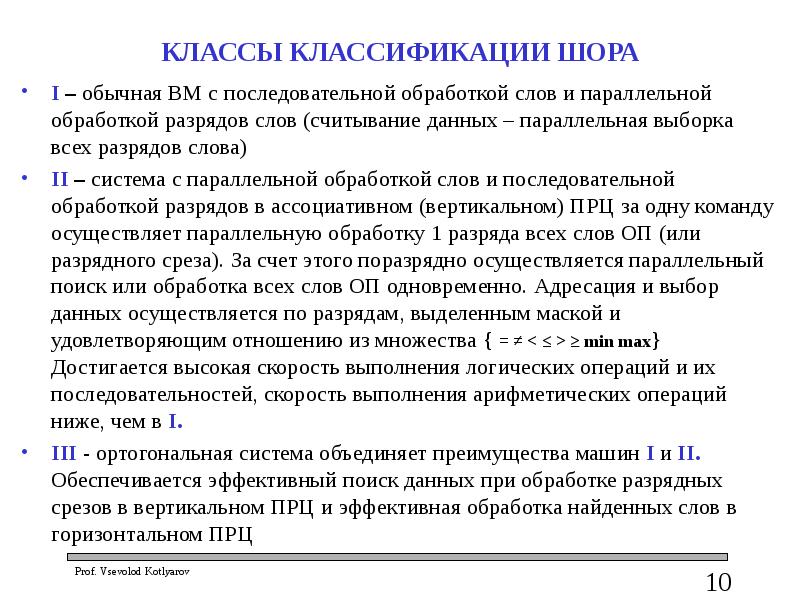

- 10. КЛАССЫ КЛАССИФИКАЦИИ ШОРА I – обычная ВМ с последовательной обработкой слов

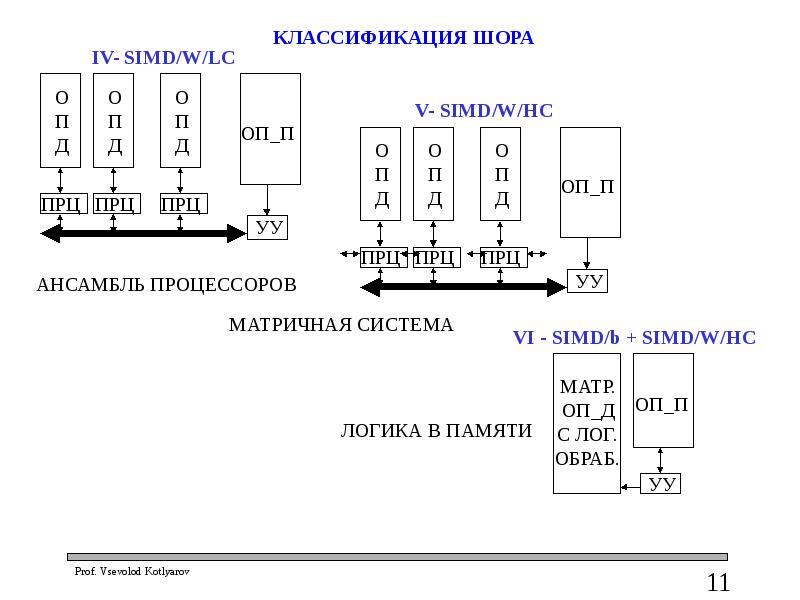

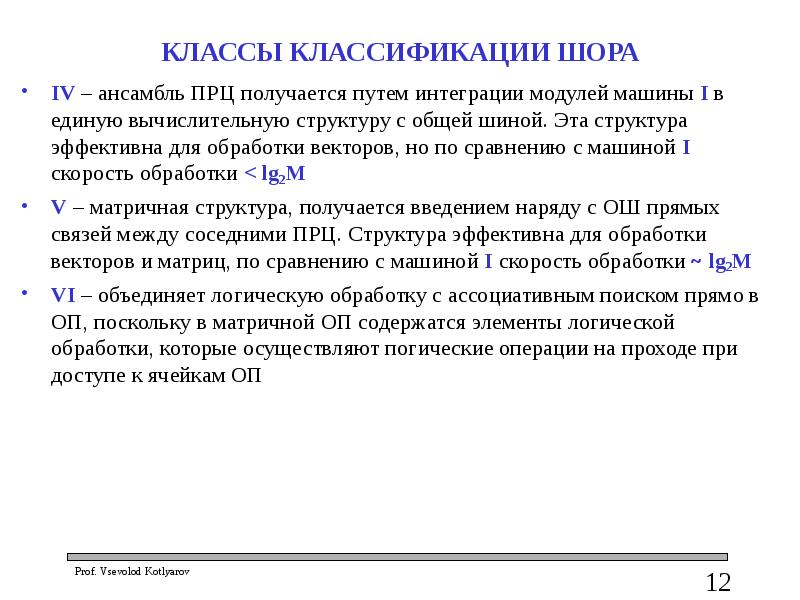

- 12. КЛАССЫ КЛАССИФИКАЦИИ ШОРА IV – ансамбль ПРЦ получается путем интеграции модулей

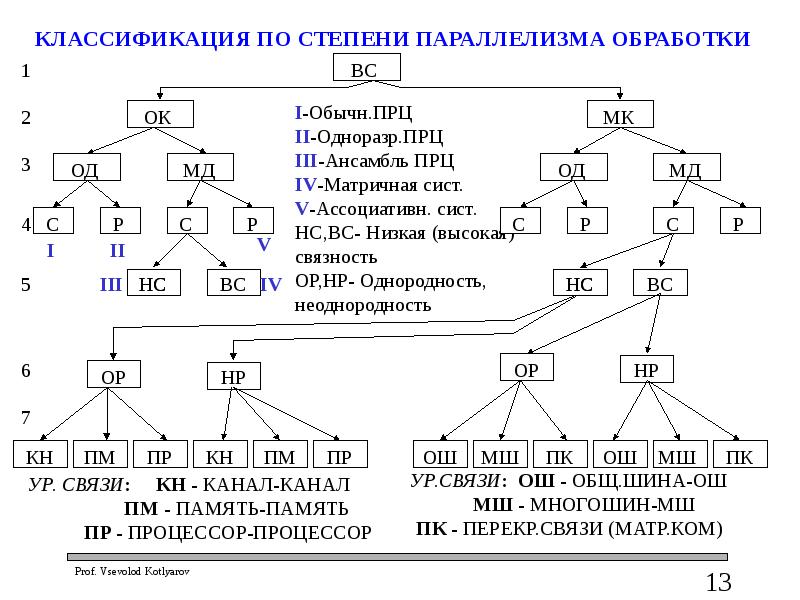

- 13. КЛАССИФИКАЦИЯ ПО СТЕПЕНИ ПАРАЛЛЕЛИЗМА ОБРАБОТКИ

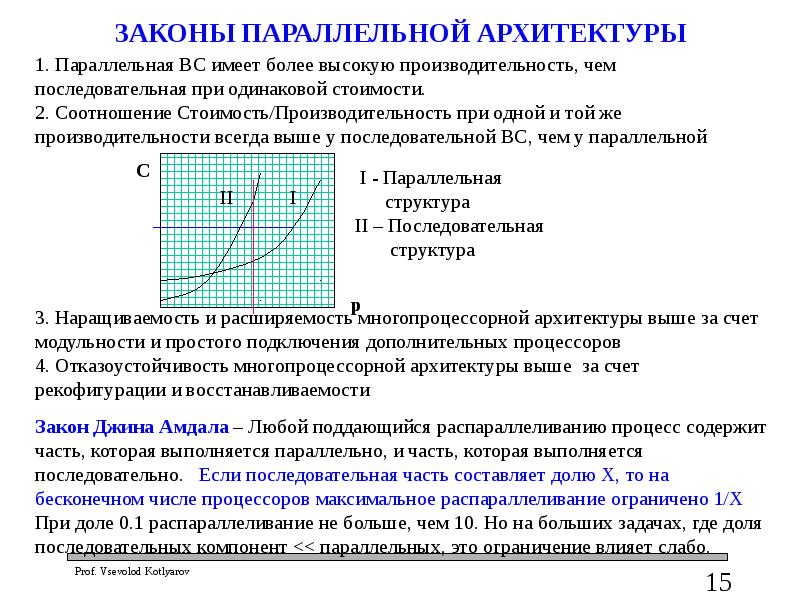

- 15. ЗАКОНЫ ПАРАЛЛЕЛЬНОЙ АРХИТЕКТУРЫ

- 16. ЗАКОНЫ ПАРАЛЛЕЛЬНОЙ АРХИТЕКТУРЫ Закон Джина Амдала в более точной формулировке:

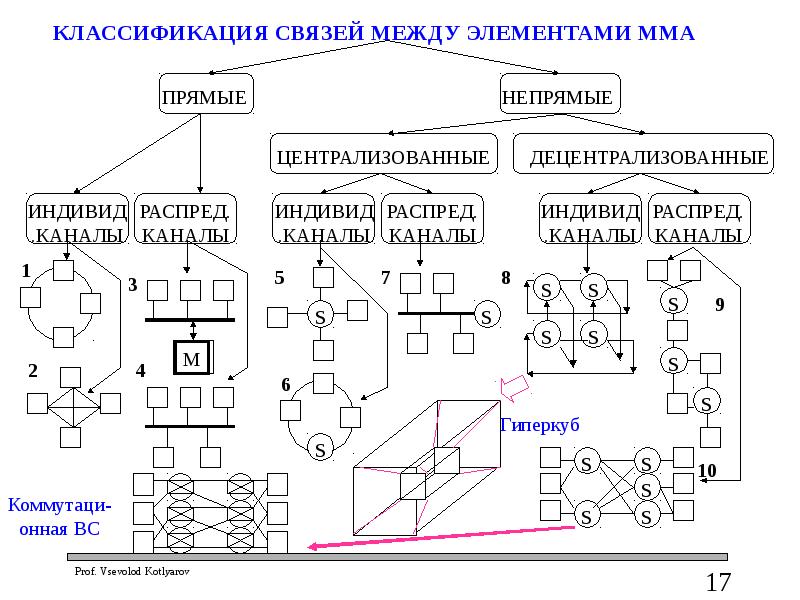

- 18. КЛАССИФИКАЦИЯ СВЯЗЕЙ МЕЖДУ ЭЛЕМЕНТАМИ ММА

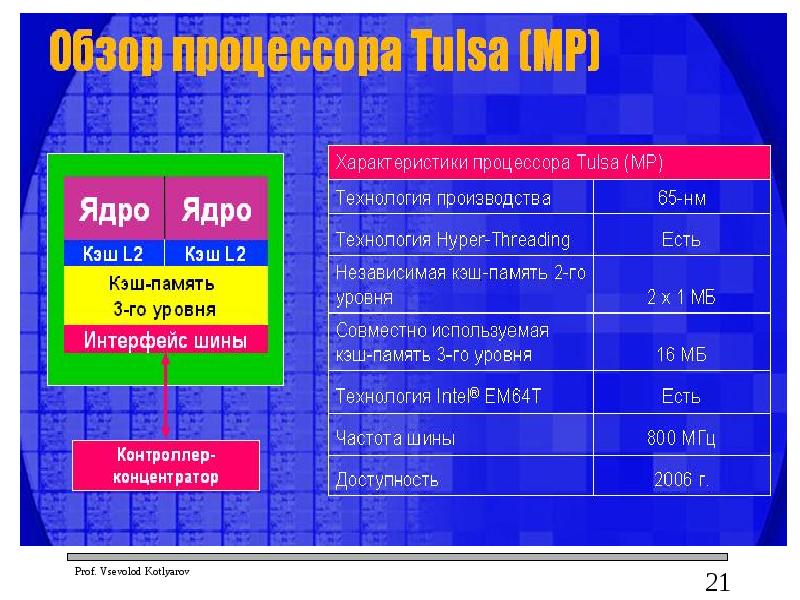

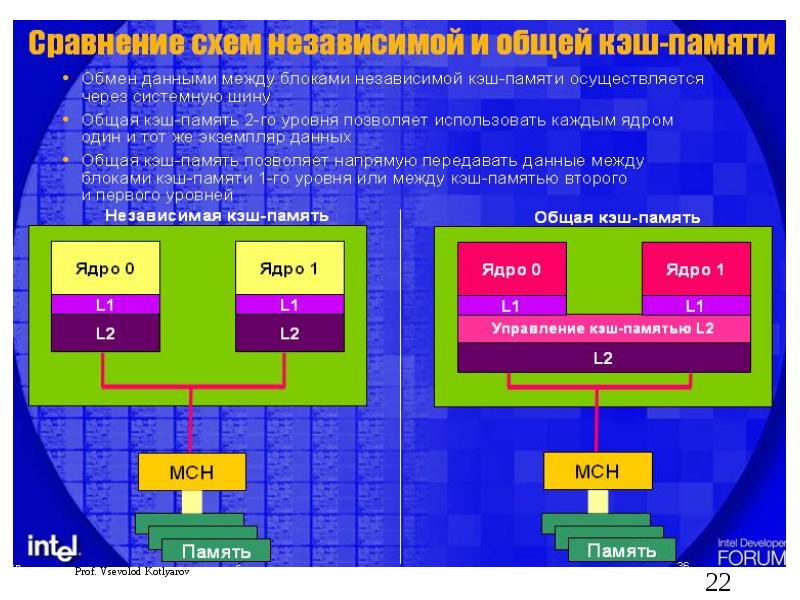

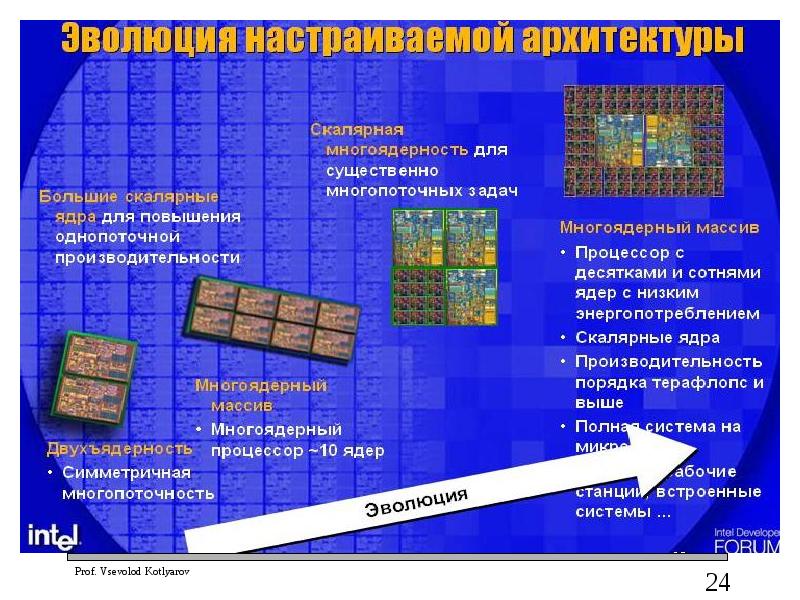

- 20. ЧТО ПОСЛЕ СУПЕРСКАЛЯРНОЙ АРХИТЕКТУРЫ СУПЕРСКАЛЯРНУЮ АРХИТЕКТУРУ сменит Мультимашинная (MultyСore)

- 25. Тест 1 Найти в интернете и распечатать описания архитектур современных ВС

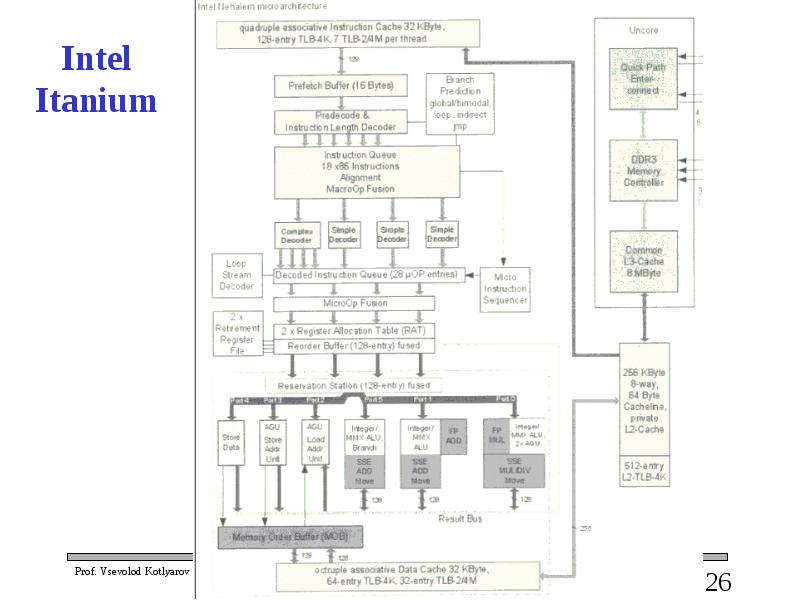

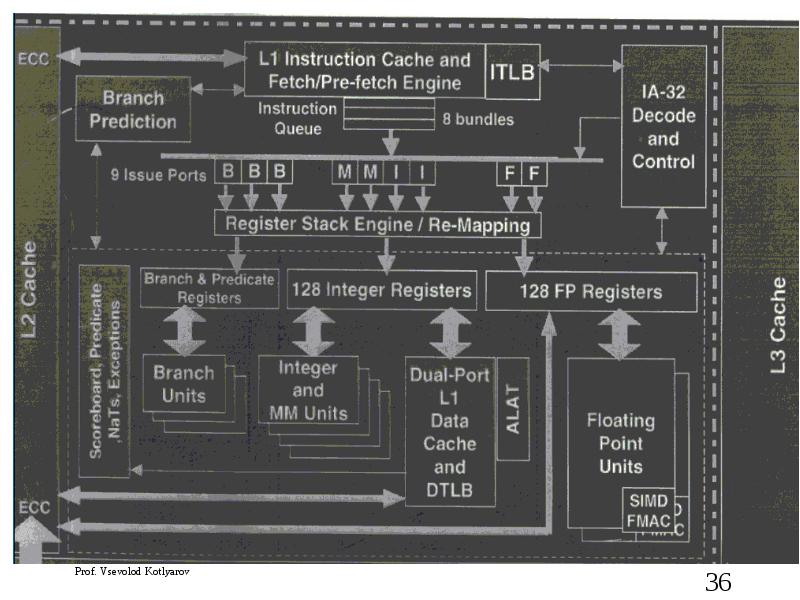

- 26. Intel Itanium

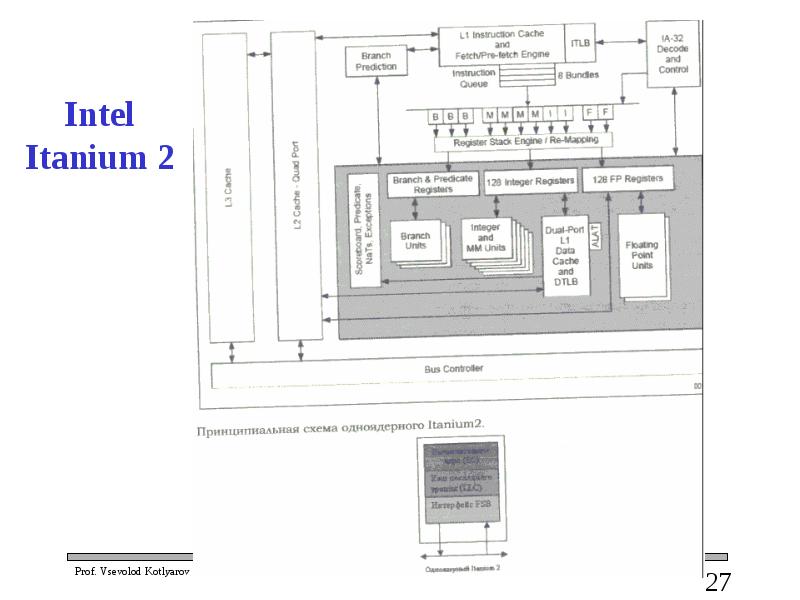

- 27. Intel Itanium 2

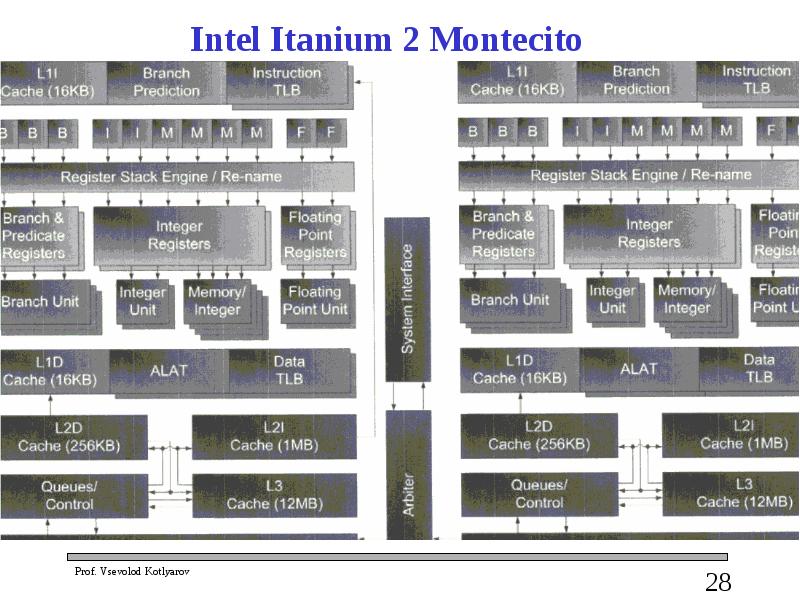

- 28. Intel Itanium 2 Montecito

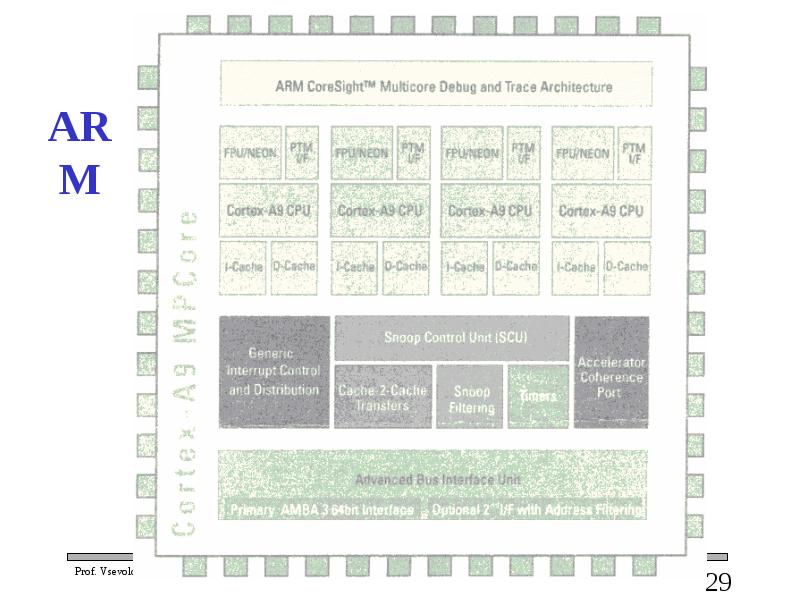

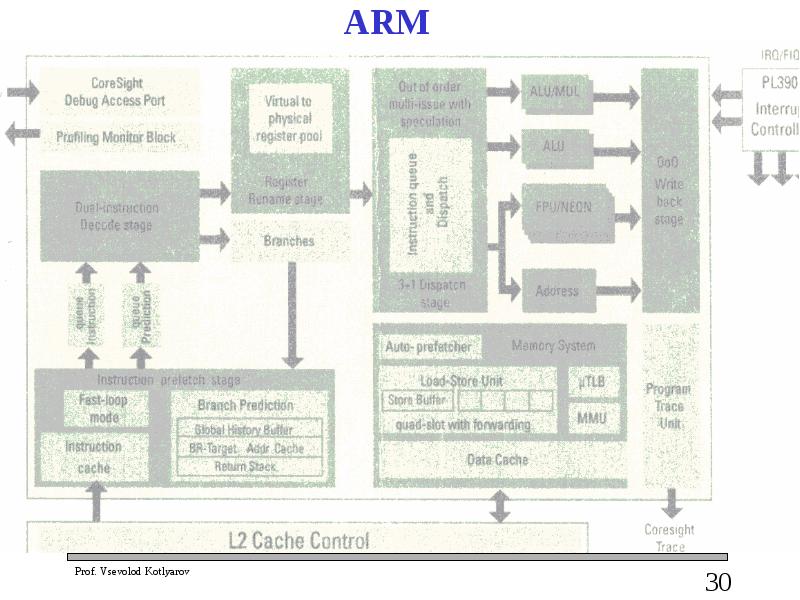

- 29. ARM

- 30. ARM

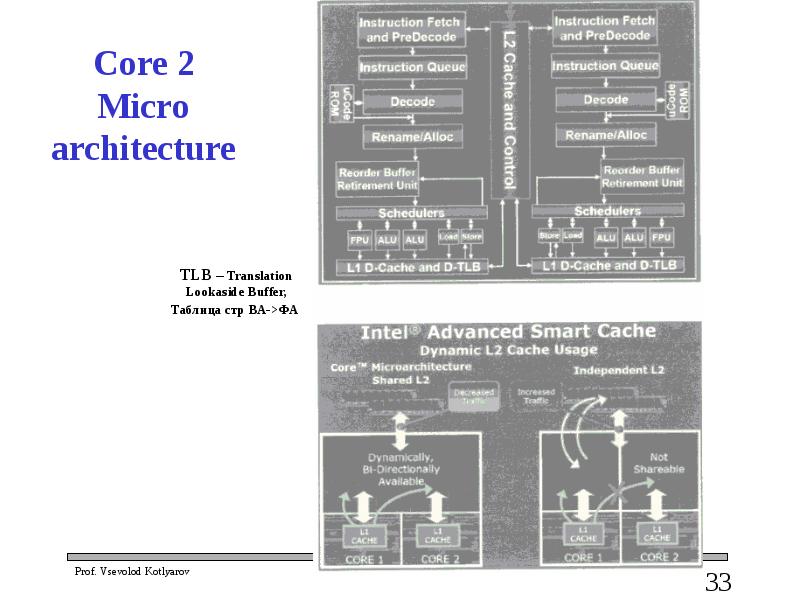

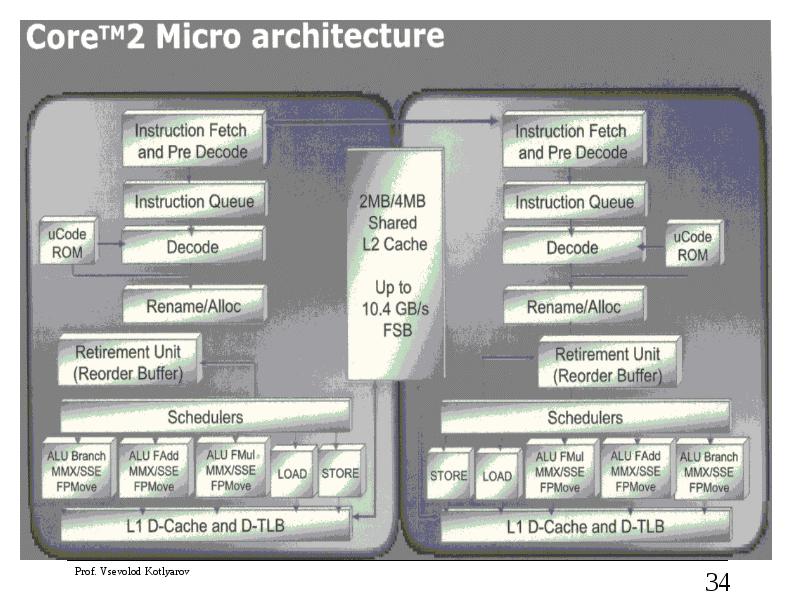

- 33. Core 2 Micro architecture

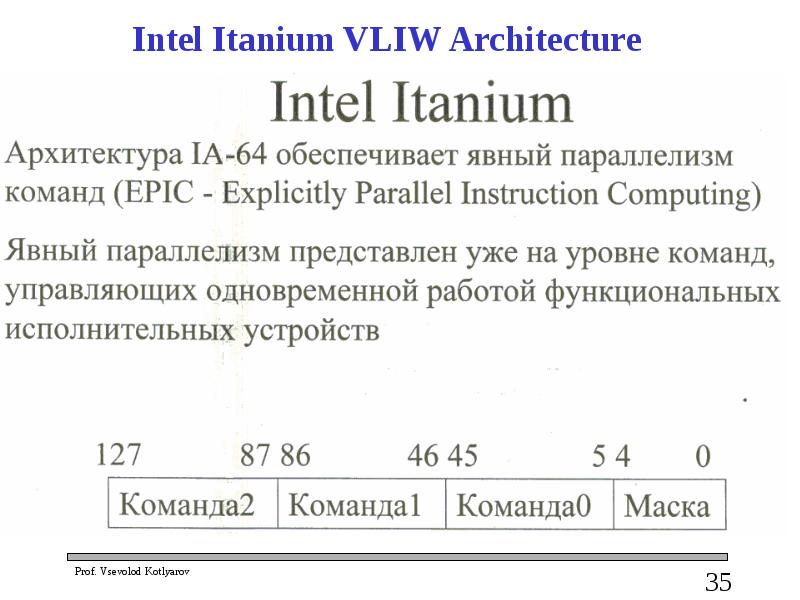

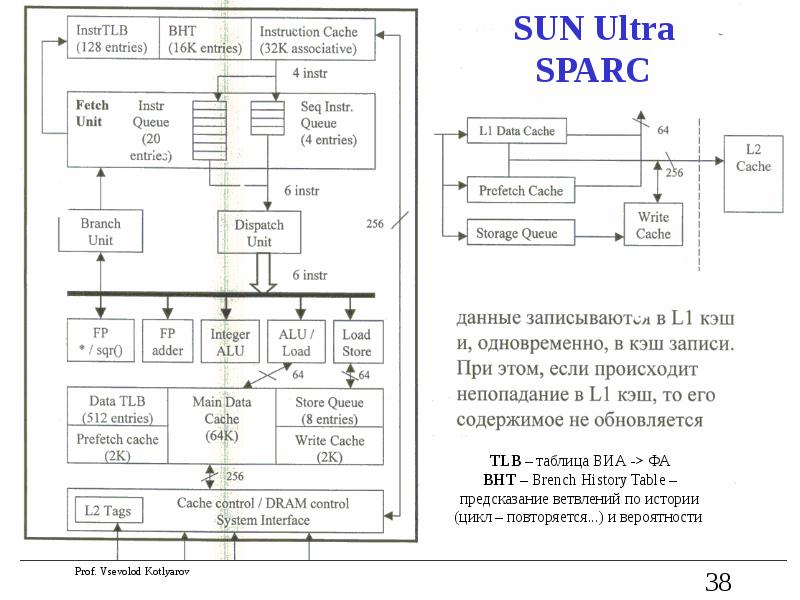

- 35. Intel Itanium VLIW Architecture

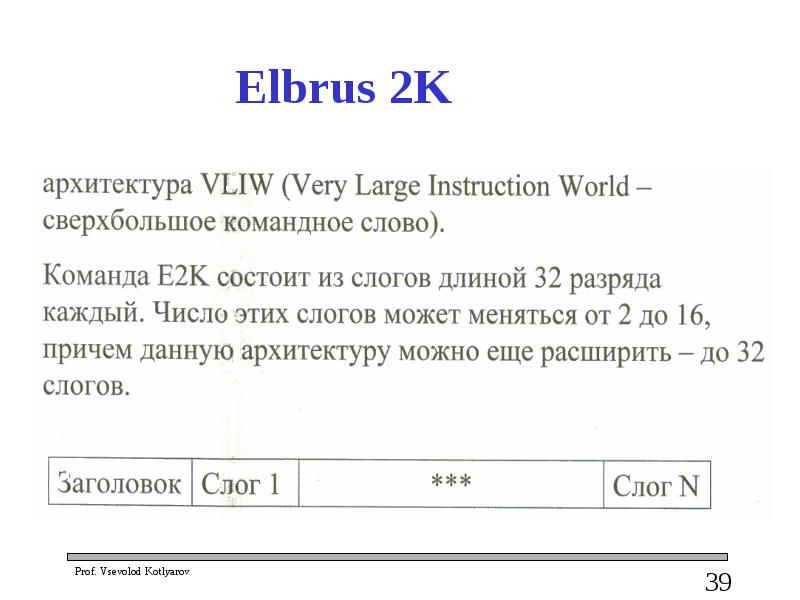

- 39. Elbrus 2K

- 40. AMD 64 Athlonex

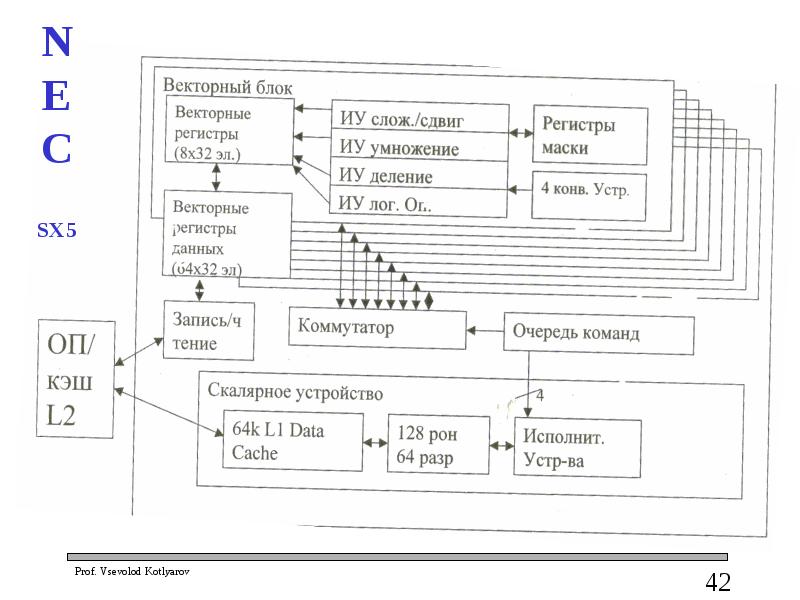

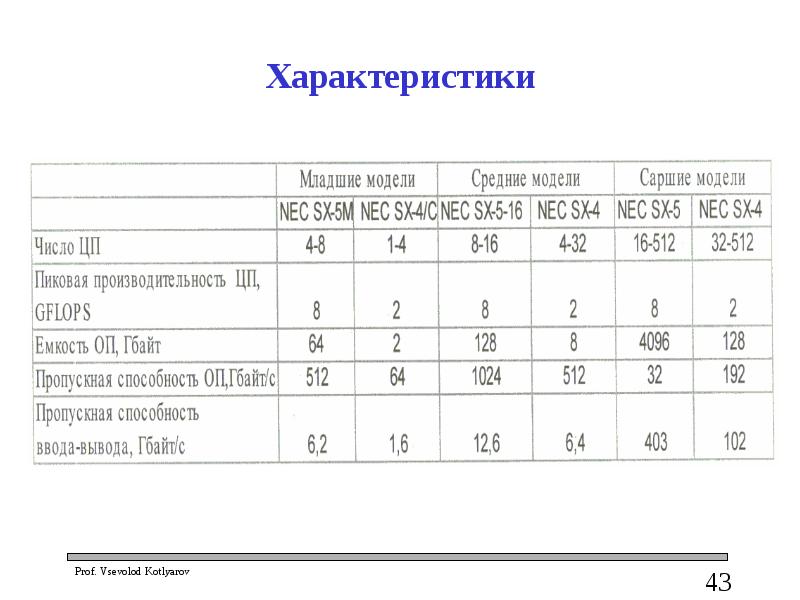

- 42. NEC SX5

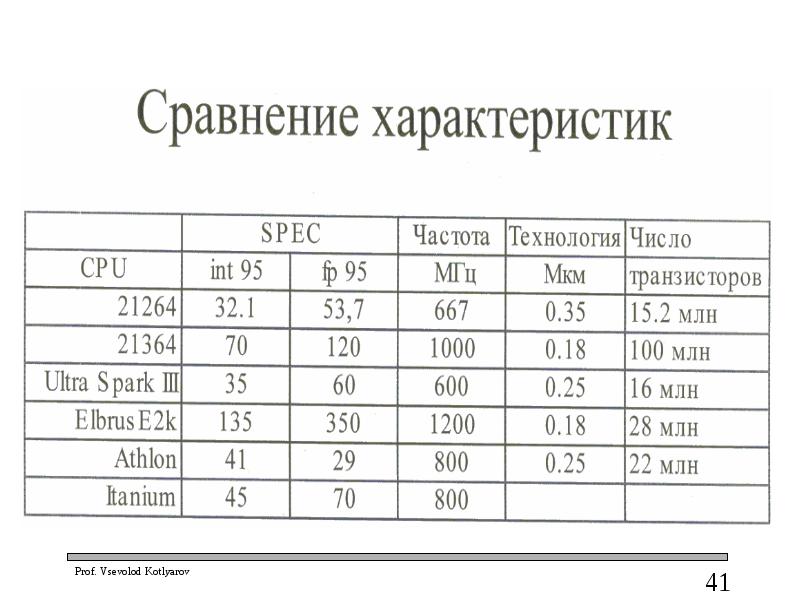

- 43. Характеристики

- 44. Скачать презентацию

Слайды и текст этой презентации

Скачать презентацию на тему Архитектура вычислительных систем. Терминология, классификационные принципы можно ниже:

Похожие презентации