Модели процессоров и их характеристики. (Лекция 4) презентация

Содержание

- 3. История процессоров фирмы Intel началась в 1971 году, когда был выпущен

- 4. Процессор Intel 4004

- 5. Процессор Intel 8080 В 1974 году появился 8-разрядный процессор Intel 8080,

- 6. На базе микропроцессора Intel 8080 компания MITS (Micro Instrumentation and Telemetry

- 7. Процессор Intel 8085 Следующим этапом стал процессор Intel 8085 (5 Мгц,

- 8. Процессор Intel 8086 Первый 16-разрядный процессор Intel 8086 фирма Intel

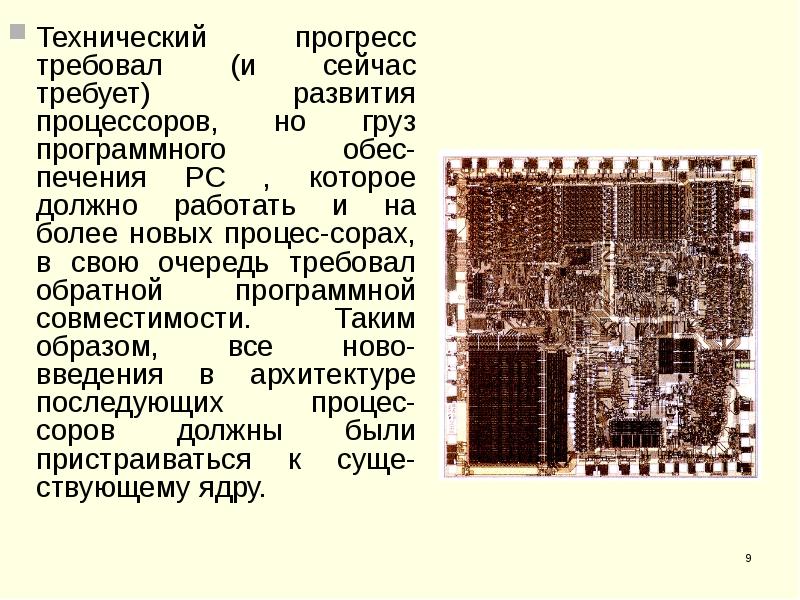

- 9. Технический прогресс требовал (и сейчас требует) развития процессоров, но груз программного

- 10. Общие сведения о процессоре Intel 8086 Процессоры 8086, выпущенные фирмой

- 11. Общие сведения о процессоре Intel 8086 Функциональные различия этих процессоров, обусловлены

- 12. Общие сведения о процессоре Intel 8086 Процессор имеет 14 регистров разрядностью

- 13. 4. Структура процессора Intel 8086 Блок-схема микропроцессора Intel 8086 представлена

- 14. Блок-схема микропроцессора Intel 8086

- 15. Процессор Intel 8086 Сигнал BHE в комбинации с сигналом на линии

- 16. Конвейер процессора Intel 8086 В процессорах применена конвейерная архитектура, позволяющая выполнить

- 18. Регистры процессора Intel 8086 Процессор имеет 14-регистров разрядностью 16 бит, объединенных

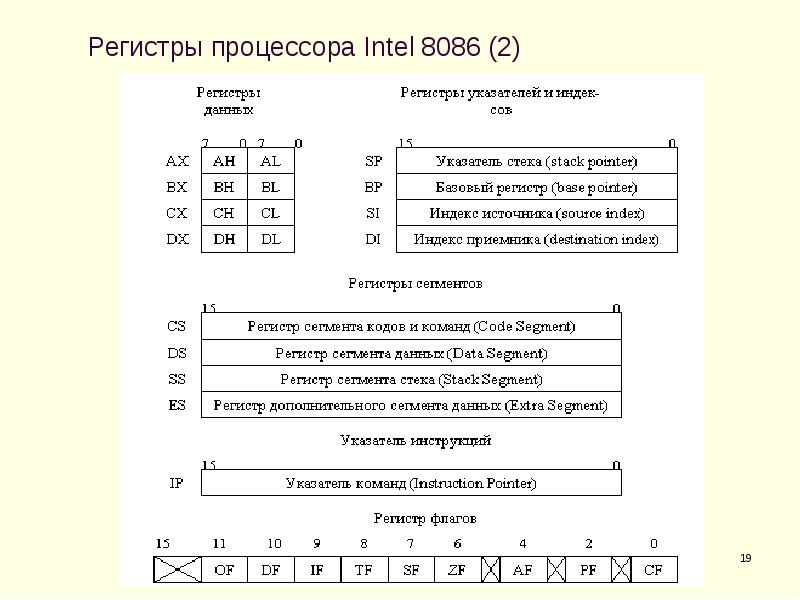

- 19. Регистры процессора Intel 8086 (2)

- 20. Регистры процессора Intel 8086 Если требуется использовать регистры общего назначения как

- 21. Регистры процессора Intel 8086 В ряде команд принято использовать те

- 22. Регистры процессора Intel 8086 Регистр флагов FLAGS хранит признаки результатов

- 23. Регистры процессора Intel 8086 IF (Interrupt Flag) – флаг управления прерываниями.

- 24. Адресация памяти и ввода/вывода Процессор предусматривает разделение пространств памяти и ввода/вывода.

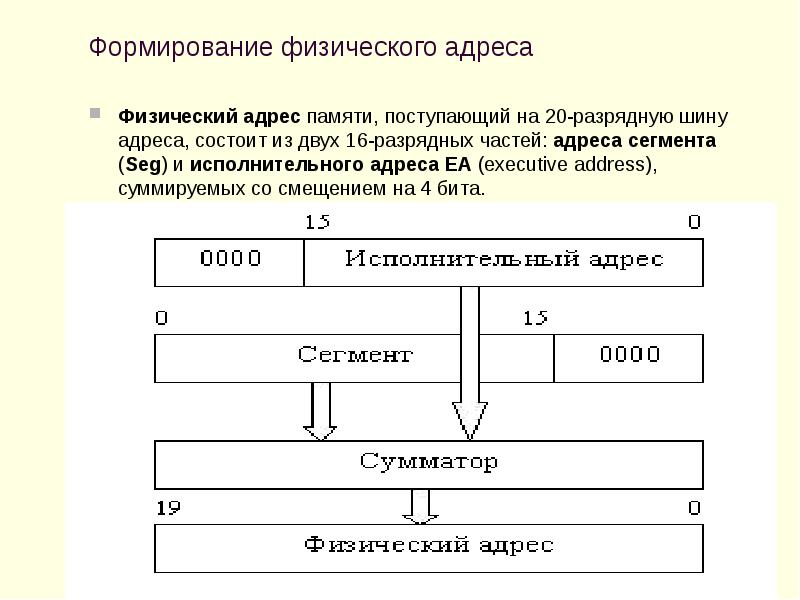

- 25. Формирование физического адреса Физический адрес памяти, поступающий на 20-разрядную шину адреса,

- 26. Ближний и дальний адрес Таким образом, при любом значении 16-битного исполнительного

- 27. Порядок L, H Все пространство памяти разбивается на параграфы – области

- 28. Сегментация Сегментация памяти, которую использовали разработчики Intel, казавшаяся на тот

- 29. Сегментация Каждая выполняющаяся программа для процессора 8086 (8088) состоит из

- 30. Сегментация Сегмент кода (Code Segment) – массив команд, предназначенных для выполнения.

- 31. Сегментация Реальный адрес требуемой ячейки памяти определяется по схеме СЕГМЕНТ:СМЕЩЕНИЕ на

- 32. Сегментация Например, в регистре SS хранится номер сегмента 0000 0011 0000

- 33. Адресация устройств ввода-вывода Пространство ввода/вывода (Input/Output Space) предназначено для обращения к

- 34. Система команд Набор команд 8086/88 включает следующие основные группы: инструкции пересылки

- 35. Прерывания Архитектура процессоров Intel 8086 предусматривает возможность прерываний – изменения последовательности

- 36. Внутренние прерывания или исключения – вырабатываются процессором при особых условиях, могущих

- 37. Программные прерывания вызываются командой INT xx и исполняются независимо от состояния

- 38. Особенности обмена по шине Цикл обмена данными между процессором 8086

- 39. Функционирование модуля интерфейса шины Тактовый генератор на системной плате (микросхема Intel

- 40. Функционирование модуля интерфейса шины Микросхема 8284A снова вырабатывает импульс (такт

- 41. Математический сопроцессор 8087 Сопроцессор 8087, официально (фирмой Intel) называемый NPX

- 42. Процессор 8088 Для процессора Intel 8086 нужно было специально разрабатывать

- 43. Процессор 8088 Некоторые компании (в частности, Godbout Electronics), выпуская клон 8088,

- 44. Процессоры 80186/80188 Процессоры i80186/80188 и их модификации 80С186/80С188 не представляют

- 45. Процессоры 80186/80188 (2) Встроенная периферия этих процессоров имеет программный интерфейс, не

- 46. Общие сведения о процессоре 80286 Процессор 80286, выпущенный в 1982 году,

- 47. Процессор может работать в двух режимах: Процессор может работать в

- 48. Переключение в защищённый режим осуществляется одной командой (с предварительно подготовленными таблицами

- 49. Совместно с процессором 80286 предусмотрена возможность использования высокопроизво-дительного математического сопроцессора 80287,

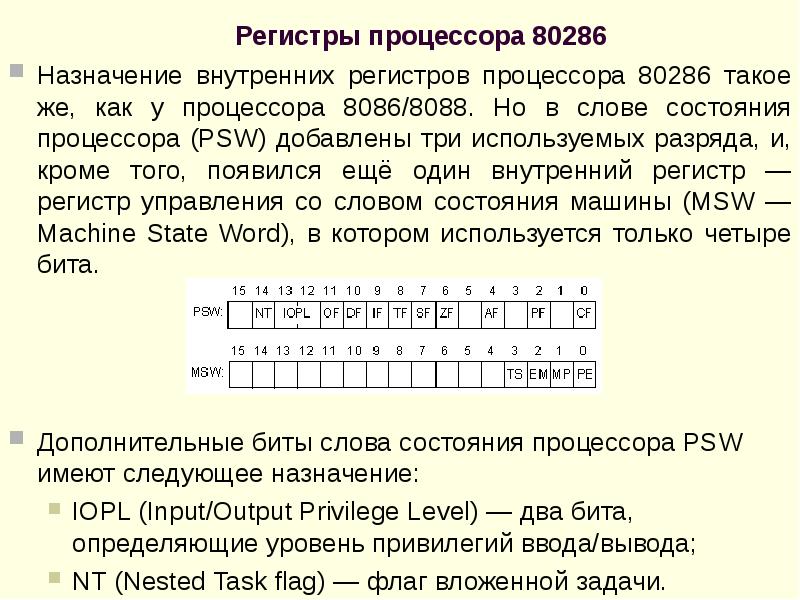

- 50. Регистры процессора 80286 Назначение внутренних регистров процессора 80286 такое же, как

- 51. Регистр MSW управляет режимом процессора. Для изменения его содержимого и сохранения

- 52. Организация памяти процессора 80286 Как и у процессоров 8086/8088, для

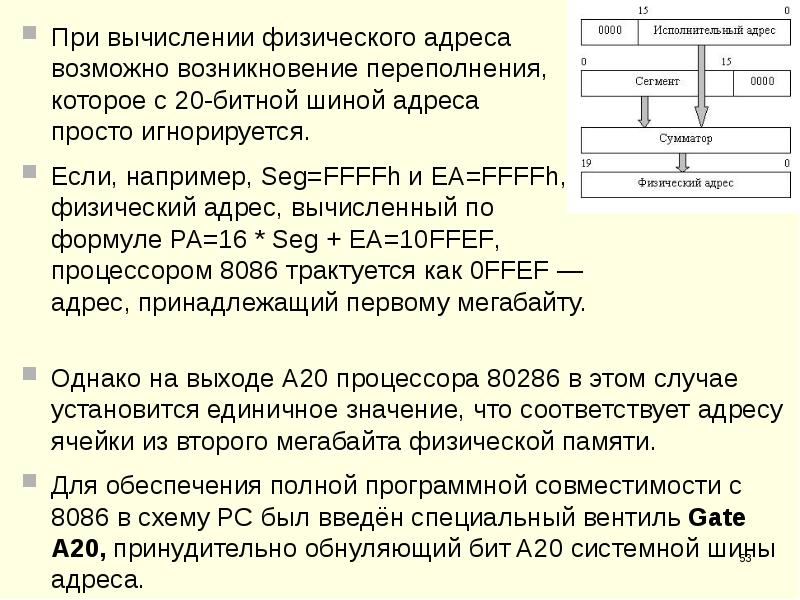

- 53. При вычислении физического адреса возможно возникновение переполнения, которое с 20-битной шиной

- 54. В защищённом режиме работают все режимы адресации, допустимые для 8086 и

- 55. Прерывания процессора 80286 Как и процессор 8086, 80286 может обрабатывать до

- 56. Каждому номеру прерывания соответствует свой элемент в таблице дескрипторов прерываний IDT

- 57. Система команд процессора 80286 Система команд процессора 80286 включает, помимо полного

- 58. Интерфейс процессора 80286 Процессоры 80286 выпускались в 68-выводных корпусах PLCC

- 59. Функционирование процессора 80286 Основными компонентами системы на базе процессора 80286 являются:

- 60. На адресную шину, состоящую из 24 линий, микропроцессор выставляет адрес байта

- 61. Микропроцессор использует шинный контроллер для формирования управляющих сигналов, определяющих передачу данных

- 62. Чтение процессором слов из оперативной памяти происходит в течение 4 тактов

- 73. Скачать презентацию

Слайды и текст этой презентации

Скачать презентацию на тему Модели процессоров и их характеристики. (Лекция 4) можно ниже:

Похожие презентации