Организация памяти. Кэш презентация

Содержание

- 2. Иерархия памяти Общая идея иерархической (много- уровневой) организации памяти

- 3. Порядок расположения уровней в иерархии С увеличением уровня иерархии должно

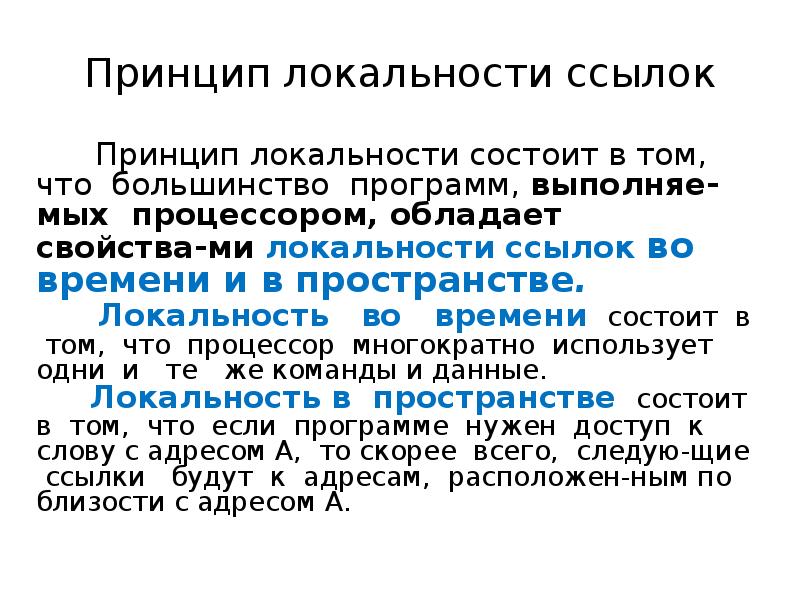

- 4. Принцип локальности ссылок

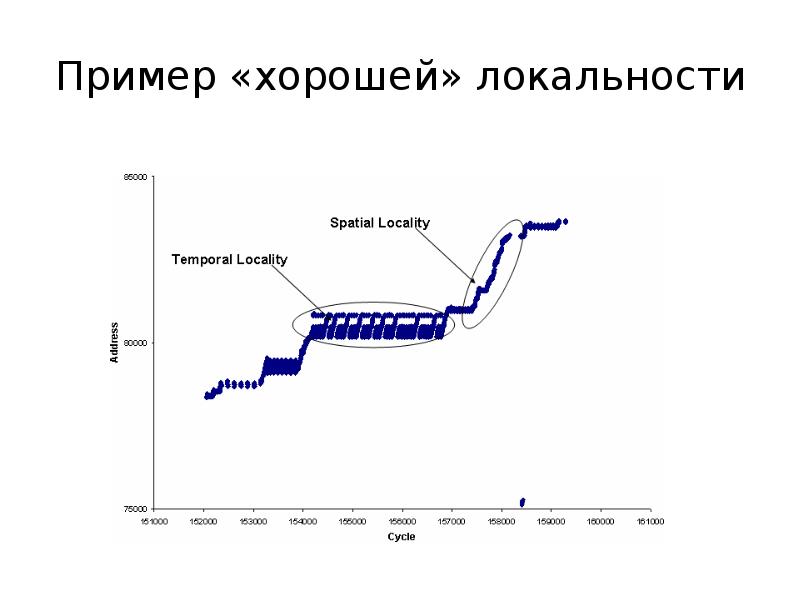

- 5. Пример «хорошей» локальности

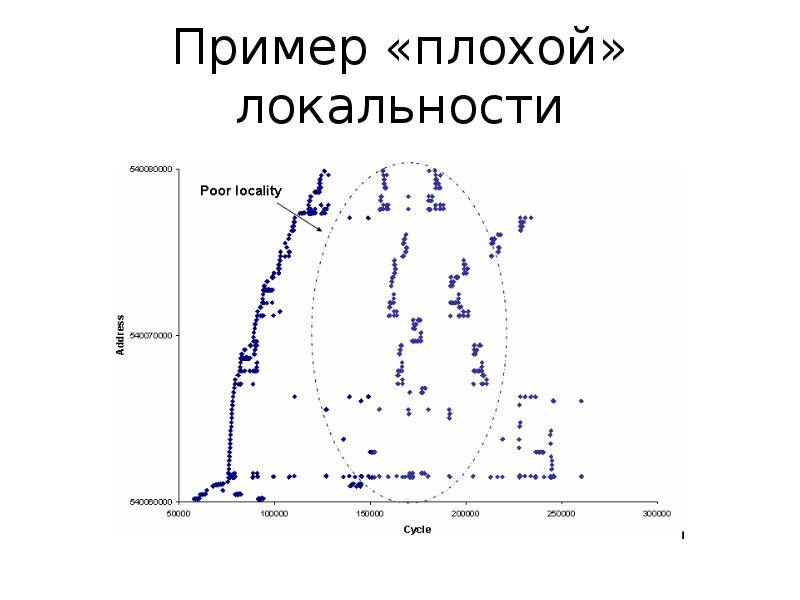

- 6. Пример «плохой» локальности

- 7. Иерархия памяти Из свойства локальности ссылок следует, что в типичном

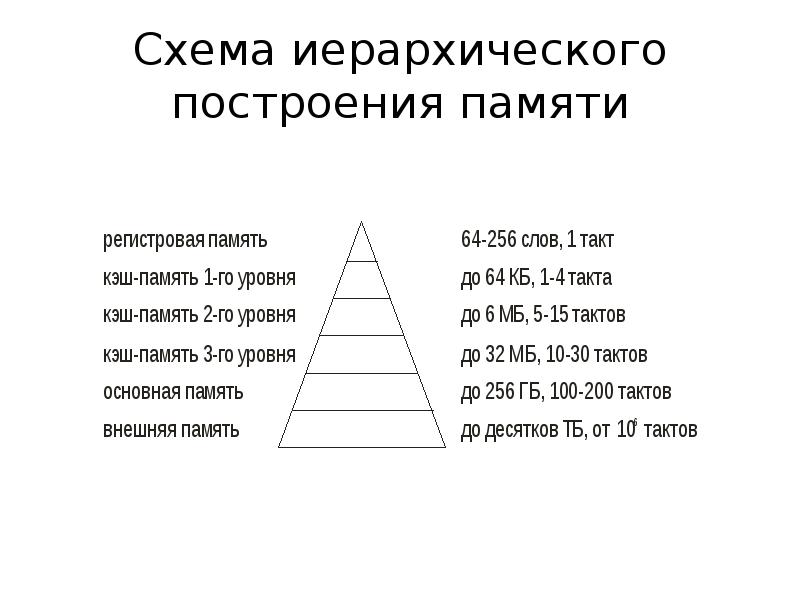

- 8. Схема иерархического построения памяти

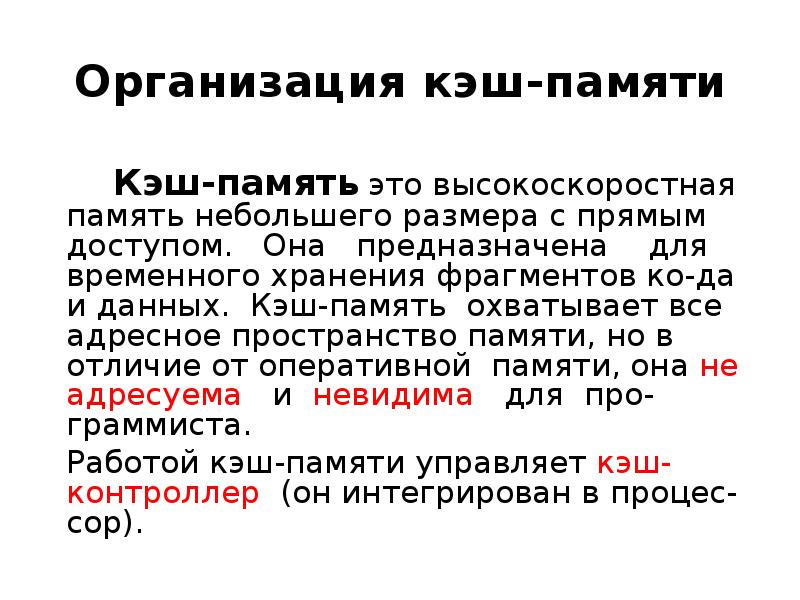

- 9. Организация кэш-памяти Кэш-память это высокоскоростная память небольшeго размера с

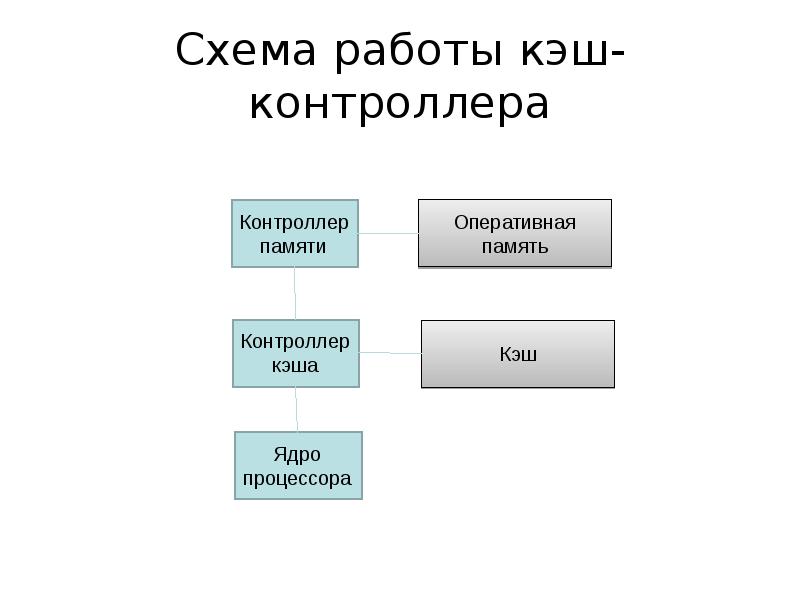

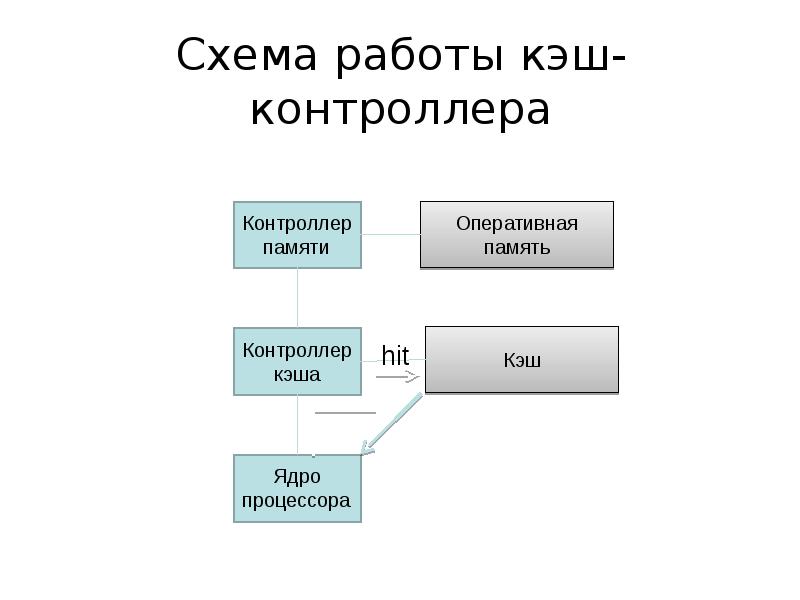

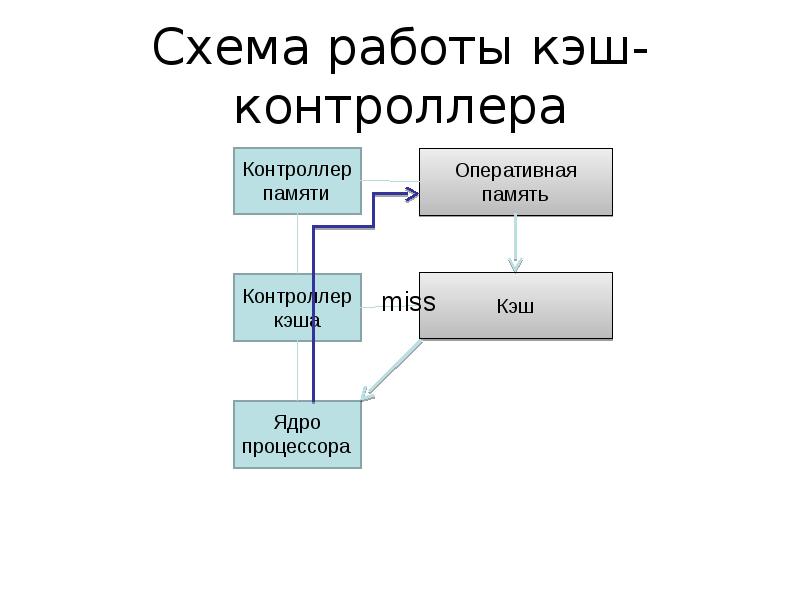

- 10. Схема работы кэш-контроллера

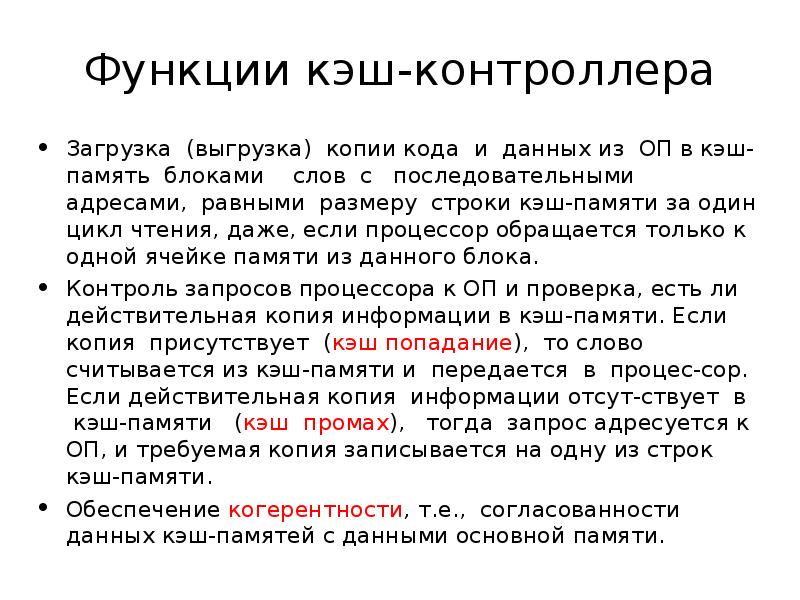

- 11. Функции кэш-контроллера Загрузка (выгрузка) копии кода и данных из ОП в

- 12. Схема работы кэш-контроллера

- 13. Схема работы кэш-контроллера

- 14. Структура кэш-памяти

- 15. Организация кэш-памяти Когда контроллер выполняет поиск данных в памяти?

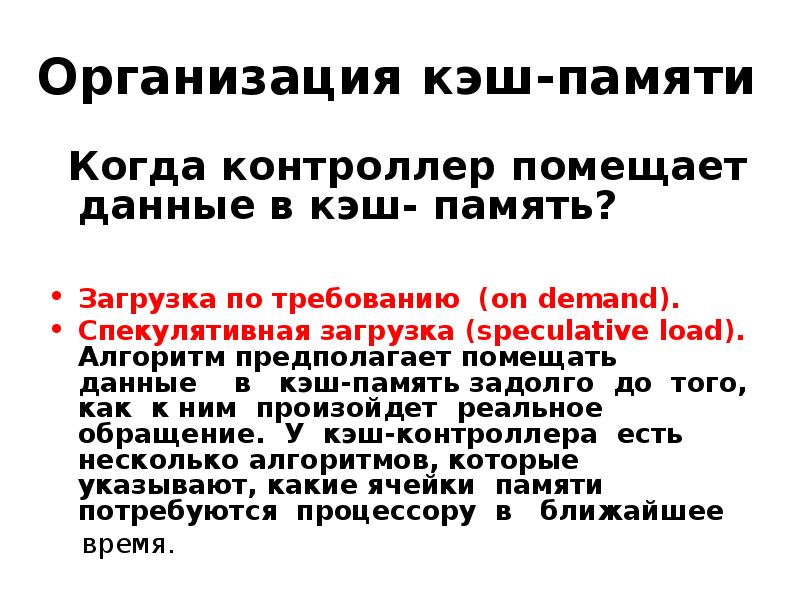

- 16. Организация кэш-памяти Когда контроллер помещает данные в кэш- память?

- 17. Основные вопросы организации кэш-памяти Алгоритм отображения адресов основной памяти в кэш-память.

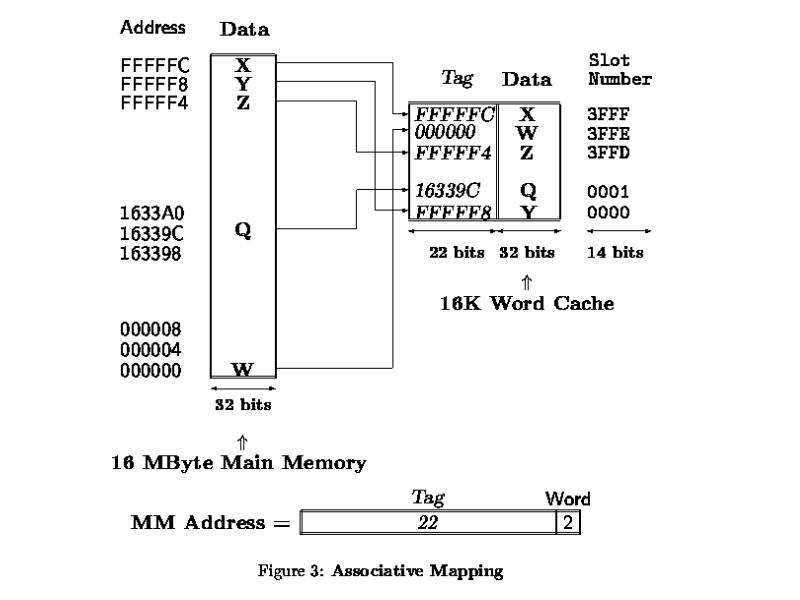

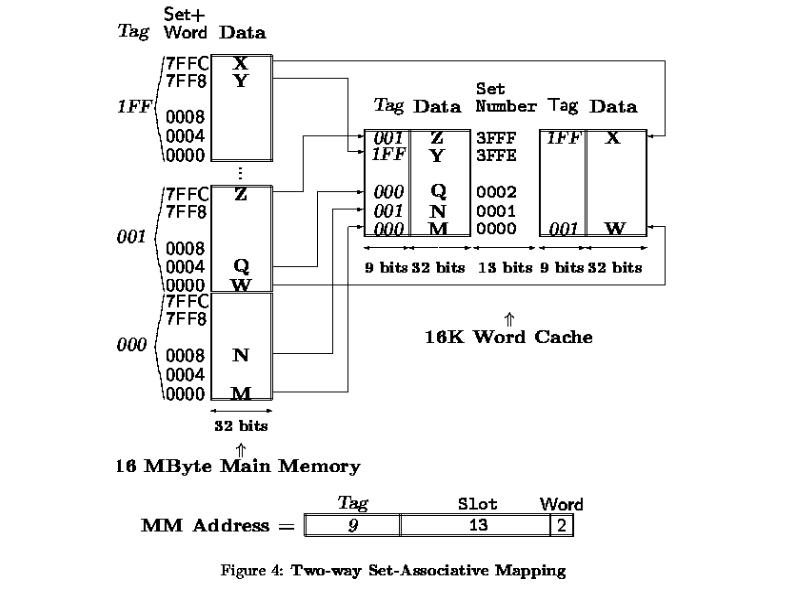

- 18. Алгоритмы отображения Прямой (direct mapping). Ассоциативный (full associative mapping).

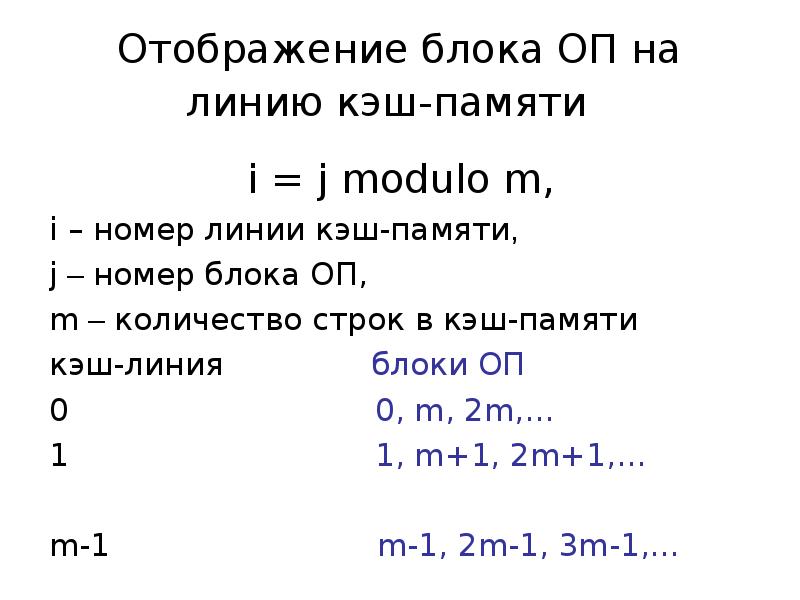

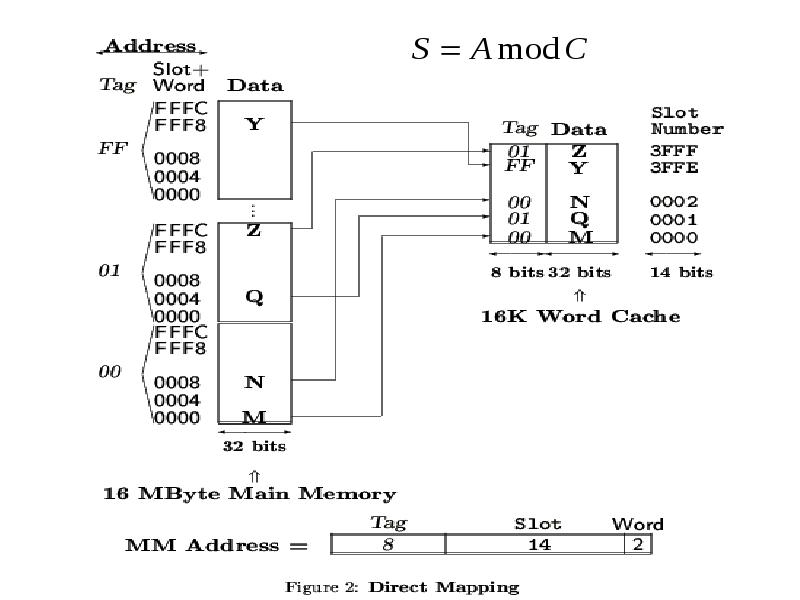

- 19. Отображение блока ОП на линию кэш-памяти i = j modulo

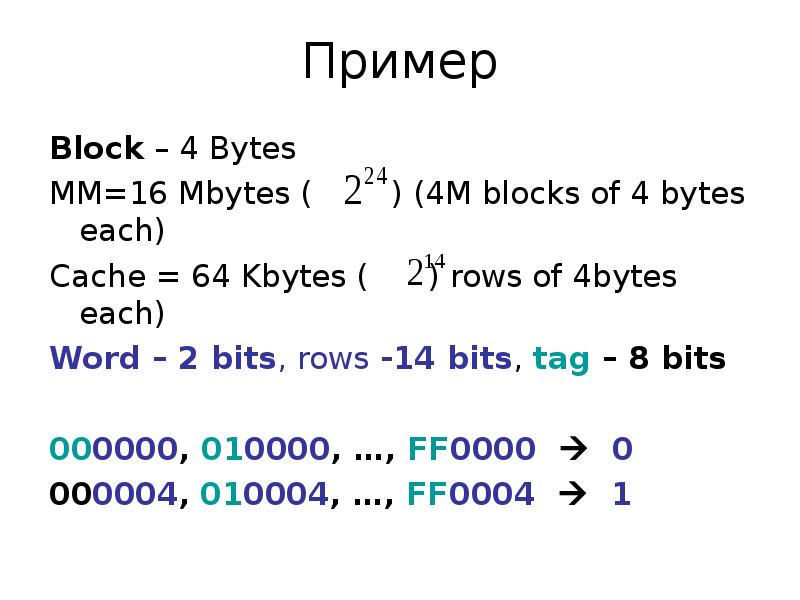

- 20. Пример Block – 4 Bytes MM=16 Mbytes ( ) (4M

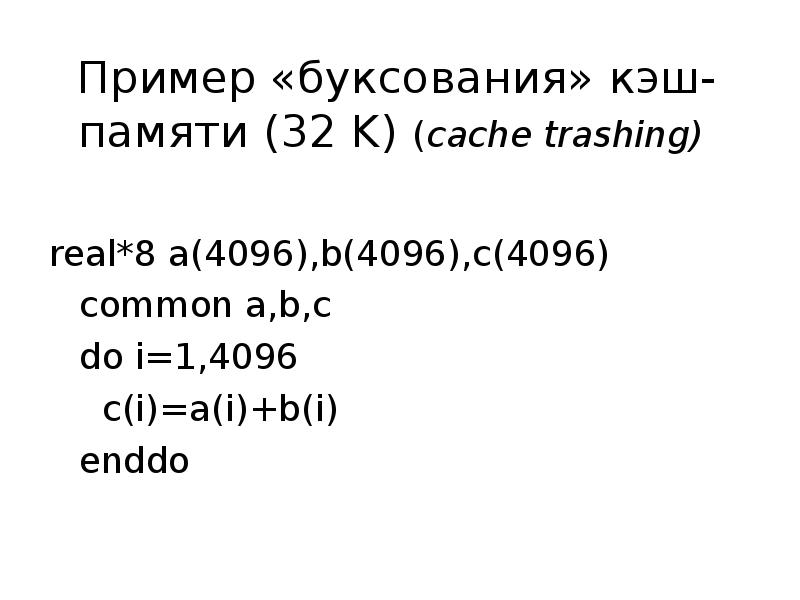

- 22. Пример «буксования» кэш-памяти (32 K) (cache trashing) real*8 a(4096),b(4096),c(4096) common

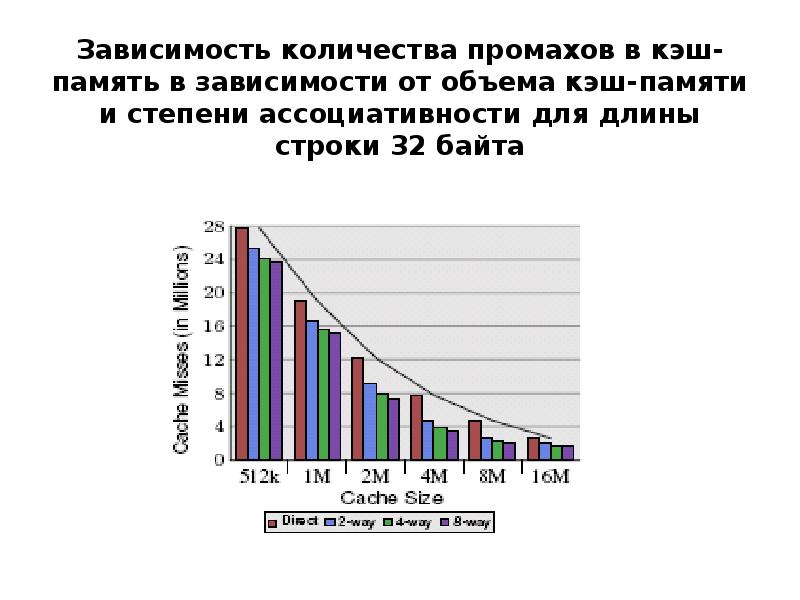

- 24. Зависимость количества промахов в кэш-память в зависимости от объема кэш-памяти и

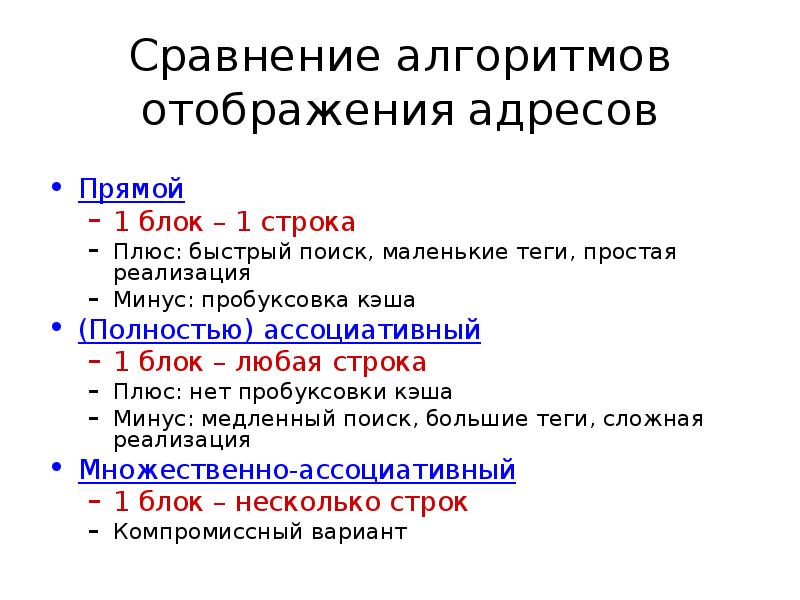

- 26. Сравнение алгоритмов отображения адресов Прямой 1 блок – 1 строка Плюс:

- 27. Алгоритмы записи Сквозная запись (Write Through (WT)). Сквозная запись с буфери-зацией

- 28. Алгоритмы замещения кэш-строк Least Recently Used (LRU) Most Recently Used (MRU)

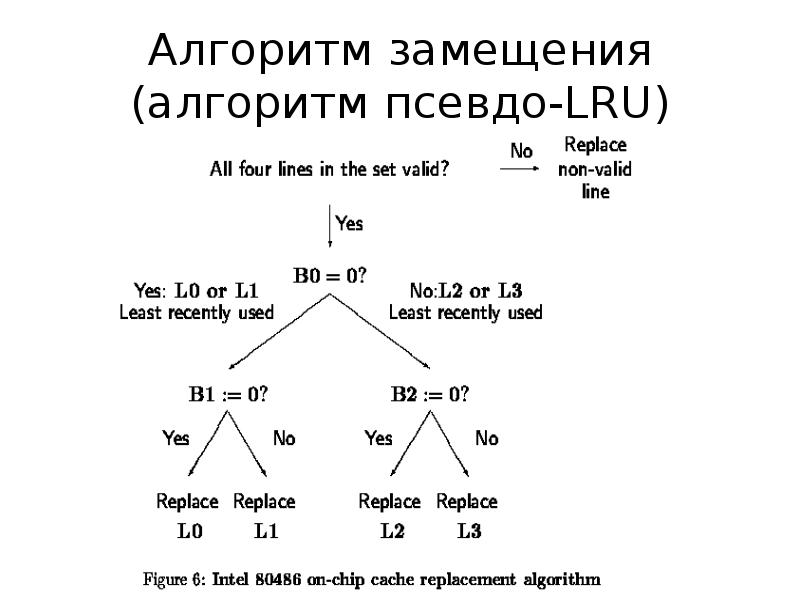

- 29. Алгоритм замещения (алгоритм псевдо-LRU)

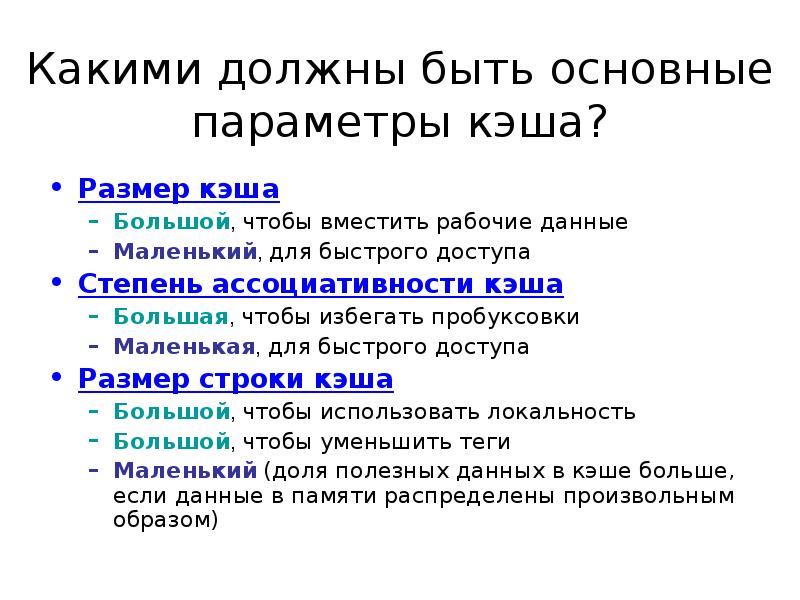

- 30. Какими должны быть основные параметры кэша? Размер кэша Большой, чтобы вместить

- 31. Предвыборка команд и данных Предвыборка команд и данных – это механизм

- 32. Два типа предвыборки Программная предвыборка (программист или компилятор явно вставляет

- 33. Скачать презентацию

Слайды и текст этой презентации

Похожие презентации