Особенности развития и структурной организации современных моделей микропроцессоров презентация

Содержание

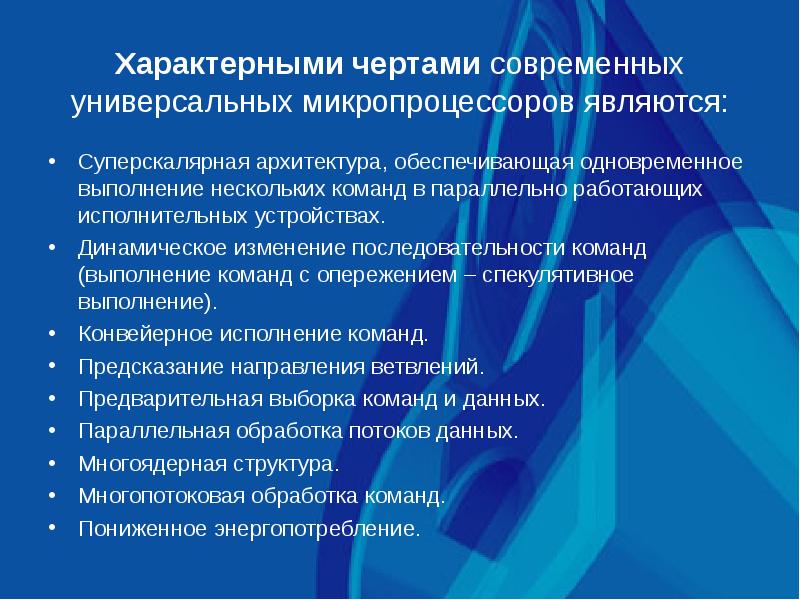

- 2. Характерными чертами современных универсальных микропроцессоров являются: Суперскалярная архитектура, обеспечивающая одновременное

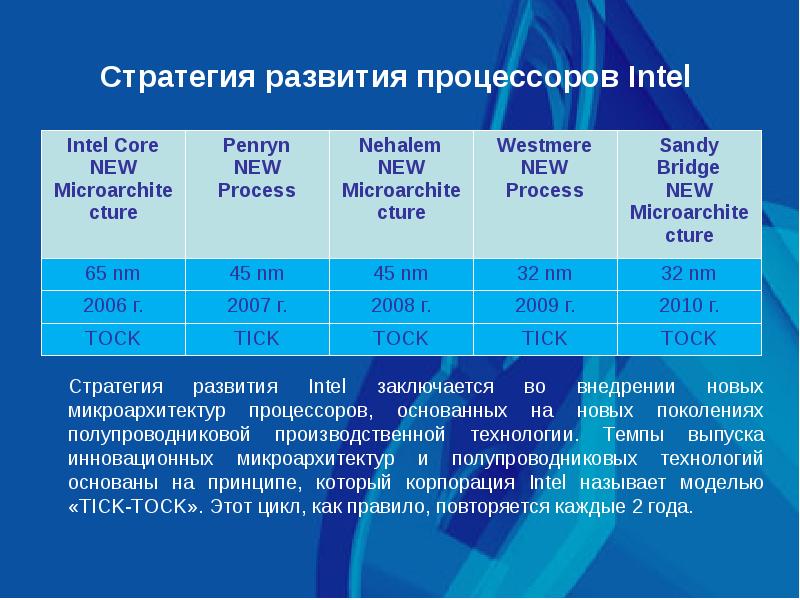

- 3. Стратегия развития процессоров Intel

- 4. Особенности многоядерной процессорной микроархитектуры Intel Core Микроархитектура Intel Core

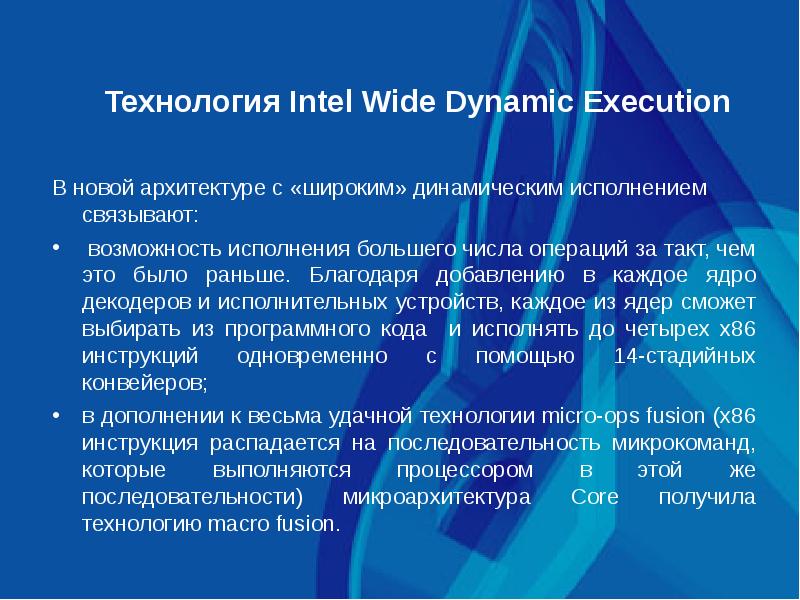

- 5. Технология Intel Wide Dynamic Execution В новой архитектуре с «широким»

- 6. Технология Intel Advanced Digital Media Boost Микроархитектура Intel

- 7. Технология Intel Advanced Smart Cache Процессоры с микроархитектурой Core имеют

- 8. Технология Intel Smart Memory Access Под этим названием объединены несколько

- 9. Технология Intel Intelligent Power Capability Главная особенность микроархитектуры Core в

- 10. Недостатки микроархитектуры Intel Core Существенным недостатком процессоров микроархитектуры Intel Core

- 11. Микроархитектура Intel Nehalem Микроархитектура Nehalem является дальнейшим развитием рассмотренной

- 12. Микроархитектура Intel Nehalem 5. Новая шина QPI с топологией точка-точка

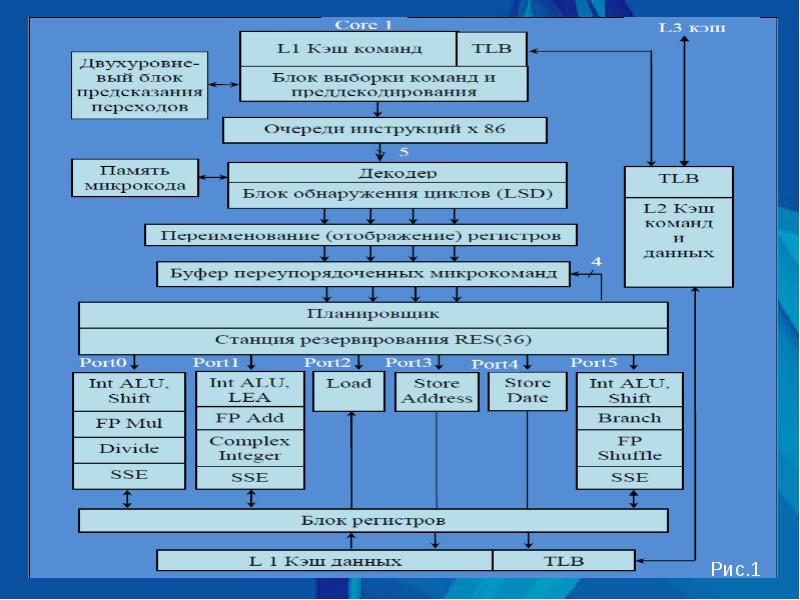

- 13. Усовершенствования вычислительного ядра Несмотря на то, что процессоры семейства

- 15. Усовершенствования вычислительного ядра Разделенные на простые и сложные х86 инструкции (Pre

- 16. Усовершенствования вычислительного ядра В Nehalem увеличилось число пар x86 команд, декодируемых

- 17. Усовершенствования вычислительного ядра Иными словами, теперь в буфере LSD сохраняются циклы

- 18. Усовершенствования вычислительного ядра Также как Core 2, в каждом ядре процессора

- 19. Усовершенствования вычислительного ядра В микроархитектуре Nehalem Intel продолжила взятый ранее курс

- 20. Новая структура кэш-памяти От двухуровневой структуры кэш-памяти в Intel Core

- 21. Реализация многопоточности Возвращение в Nehalem технологии SMT – одно из

- 22. Интегрированный в процессор контроллер памяти Nehalem стала первой интеловской микроархитектурой,

- 23. Новая процессорная шина QPI Микроархитектура Nehalem универсальна, она используется как

- 24. Модульная структура процессора Важным нововведением в Nehalem стал модульный дизайн

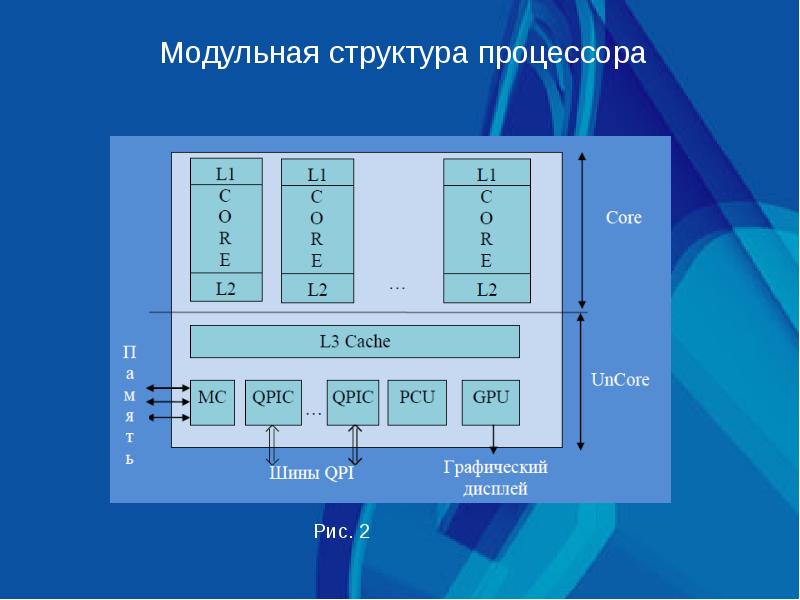

- 25. Модульная структура процессора

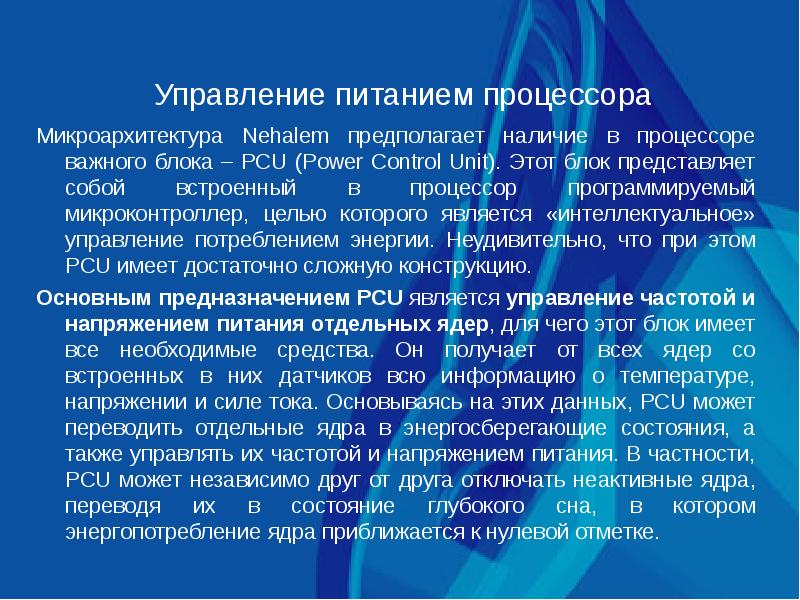

- 26. Управление питанием процессора Микроархитектура Nehalem предполагает наличие в процессоре важного

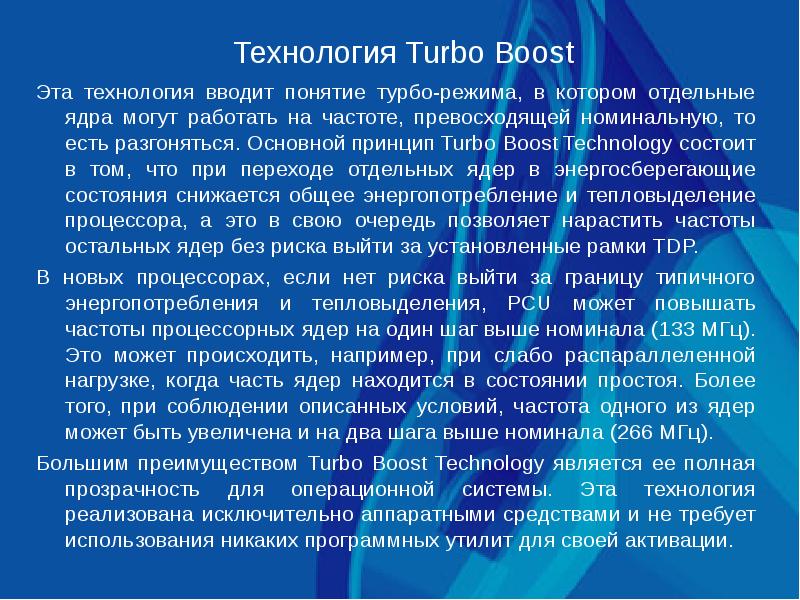

- 27. Технология Turbo Boost Эта технология вводит понятие турбо-режима, в котором

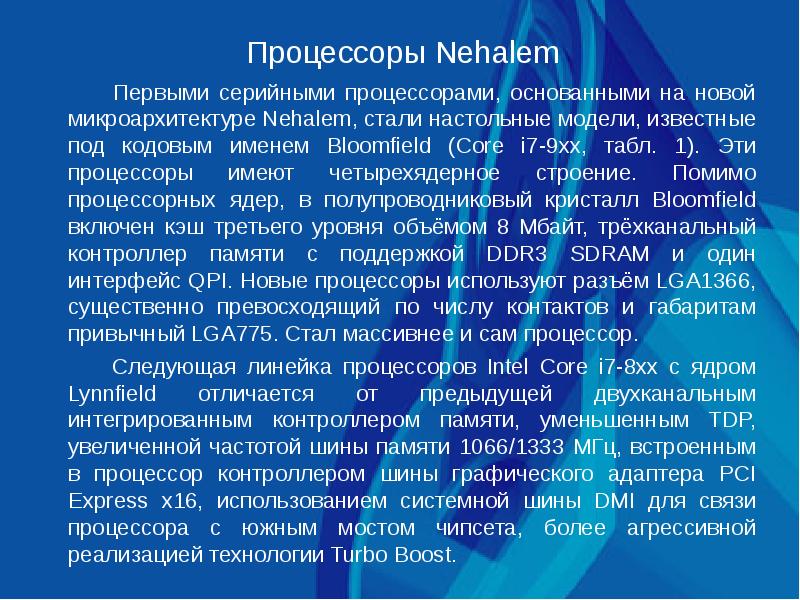

- 28. Процессоры Nehalem Первыми серийными процессорами, основанными на новой

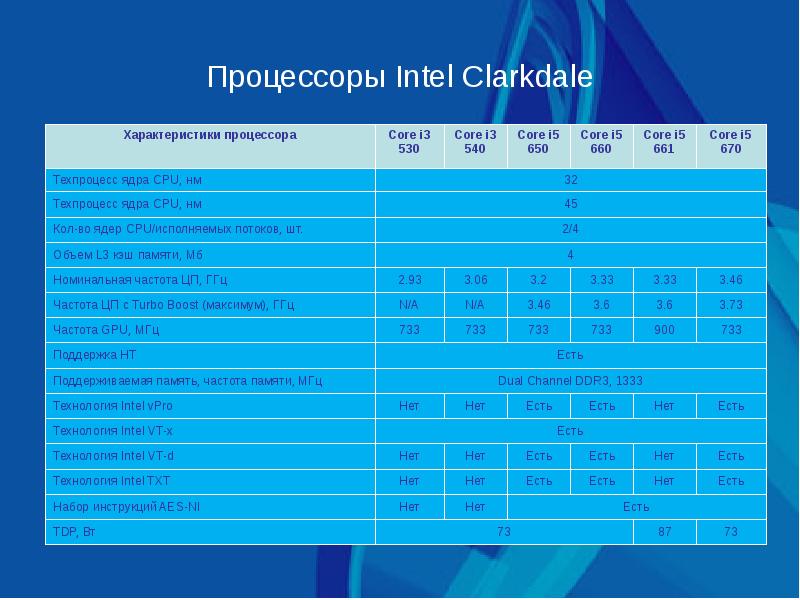

- 29. Процессоры Intel Clarkdale

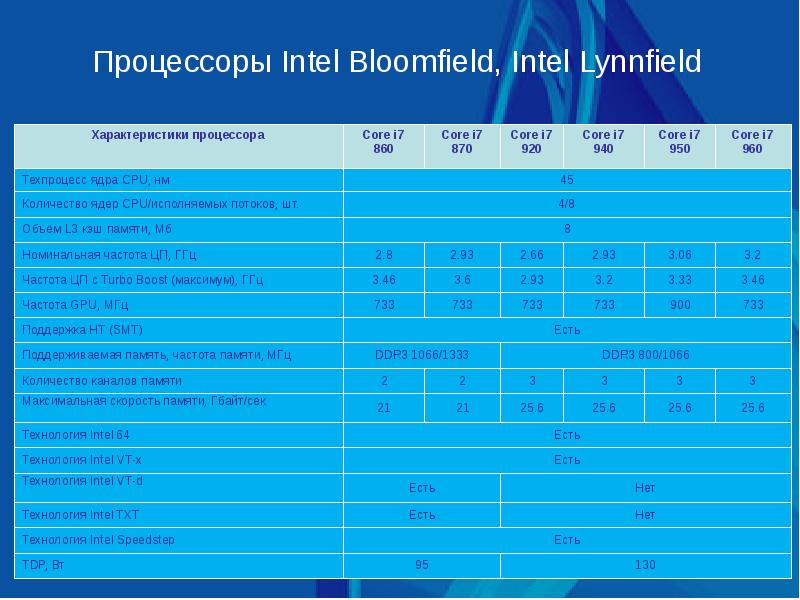

- 30. Процессоры Intel Bloomfield, Intel Lynnfield

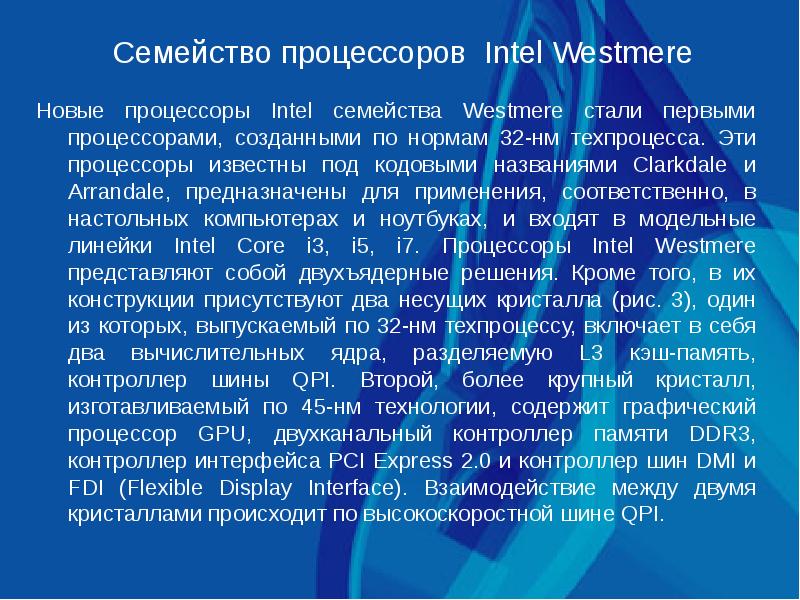

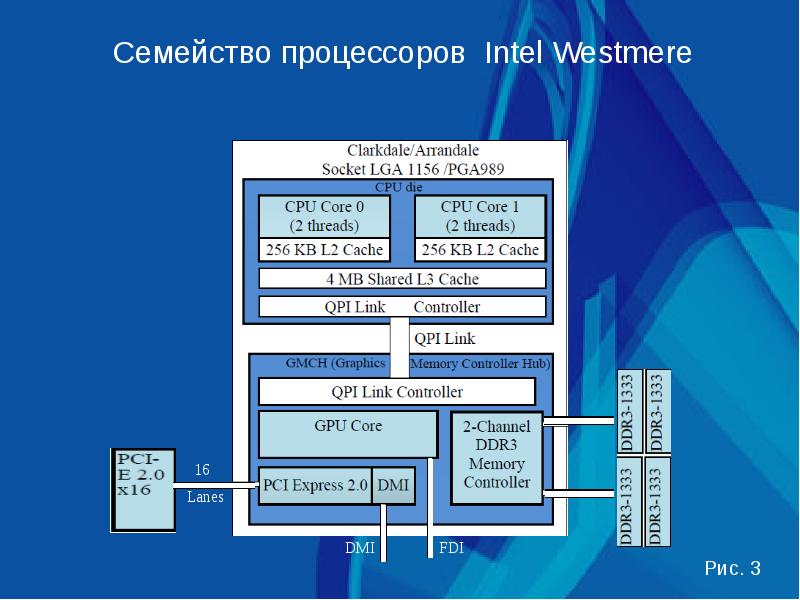

- 31. Семейство процессоров Intel Westmere Новые процессоры Intel семейства Westmere стали

- 32. Семейство процессоров Intel Westmere

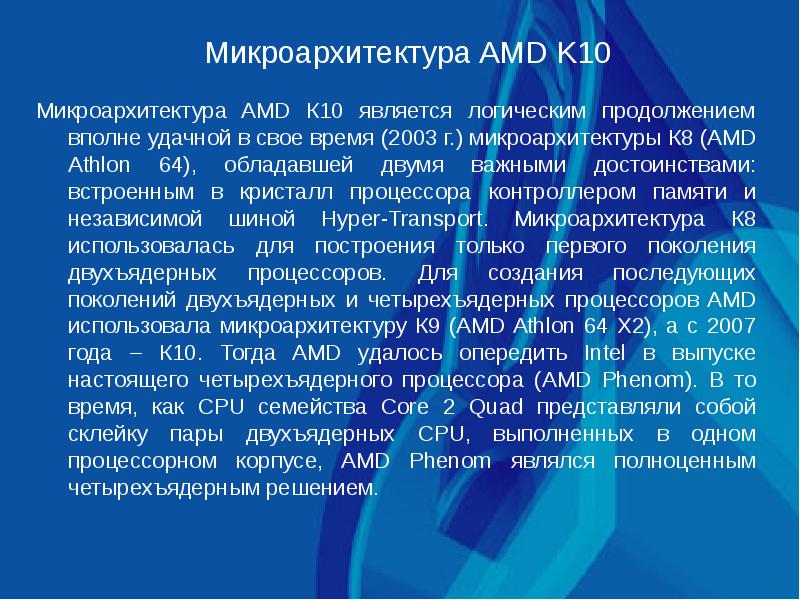

- 33. Микроархитектура AMD K10 Микроархитектура AMD К10 является логическим продолжением вполне

- 34. Микроархитектура AMD K10 Впрочем, компоновка четырех процессорных ядер на одном кристалле

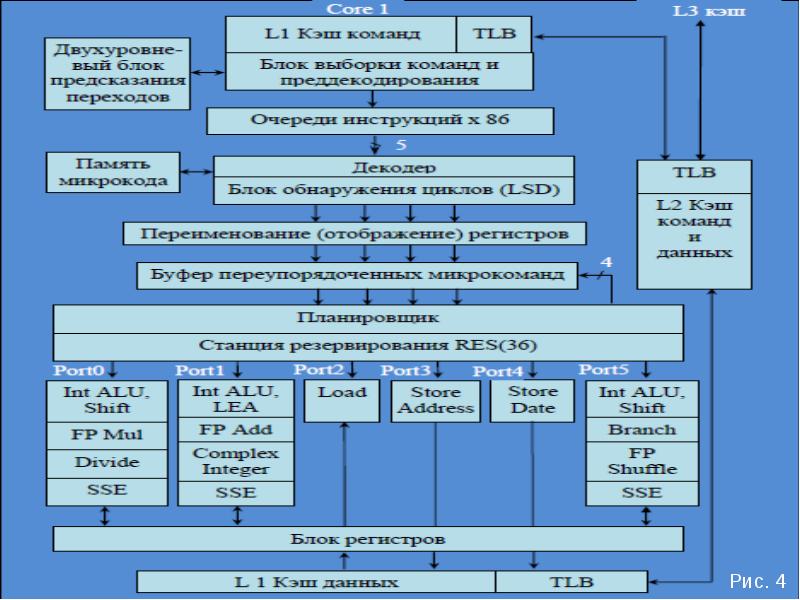

- 35. Структура ядра процессора AMD K10 Каждое ядро процессора имеет выделенный кэш

- 37. Структура ядра процессора AMD K10 В К10 предсказание переходов (Branch Prediction

- 38. Структура ядра процессора AMD K10 В процессоре К10 внешние х86-команды декодируются

- 39. Структура ядра процессора AMD K10 Аппаратный декодер Direct Path является трехканальным

- 40. Структура ядра процессора AMD K10 Микрооперации, полученные в результате декодирования инструкций

- 41. Структура ядра процессора AMD K10 Если посмотреть на схему декодера в

- 42. Структура ядра процессора AMD K10 После прохождения декодера микрооперации (по три

- 43. Структура ядра процессора AMD K10 Просматривая все 36 поступающих инструкций, FP-Renamer

- 44. Структура ядра процессора AMD K10 После того, как все микрооперации прошли

- 45. Структура ядра процессора AMD K10 В процессоре К8 после вычисления на

- 46. Структура ядра процессора AMD K10 Для работы с вещественными числами реализовано

- 47. Структура ядра процессора AMD K10 Одной из основных составляющих микроархитектур К8,

- 48. Скачать презентацию

Слайды и текст этой презентации

Скачать презентацию на тему Особенности развития и структурной организации современных моделей микропроцессоров можно ниже:

Похожие презентации