Overview презентация

Содержание

- 2. Alternative Ways to Implement Processor FSMs "Random Logic" based on Moore

- 3. Random Logic Perhaps poor choice of terms for "classical" FSMs Contrast

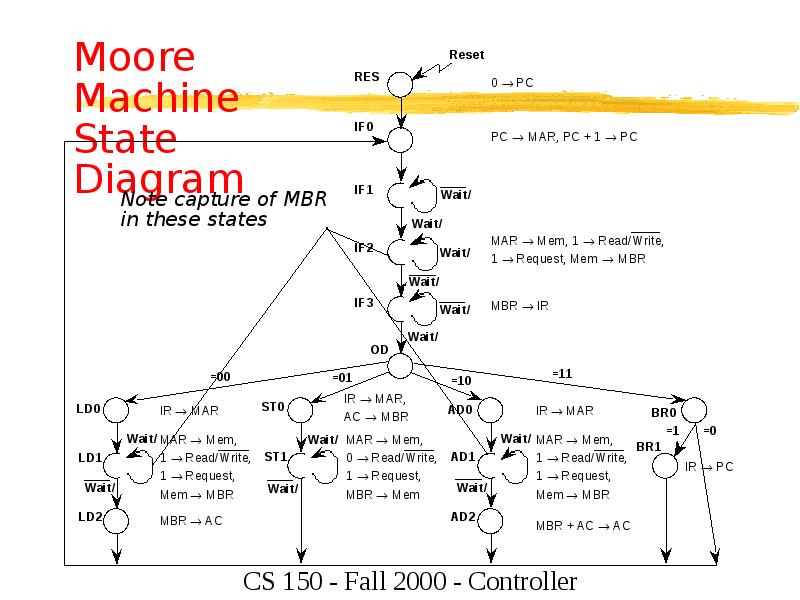

- 4. Moore Machine State Diagram

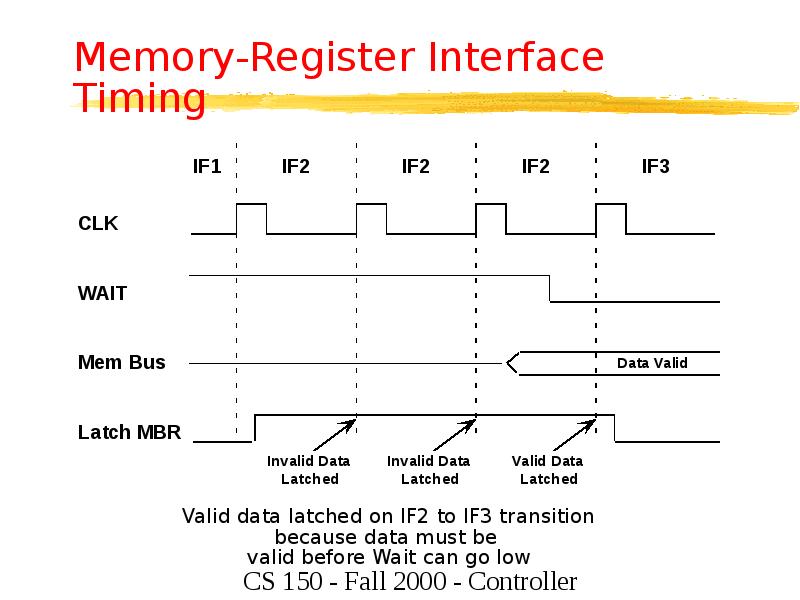

- 5. Memory-Register Interface Timing

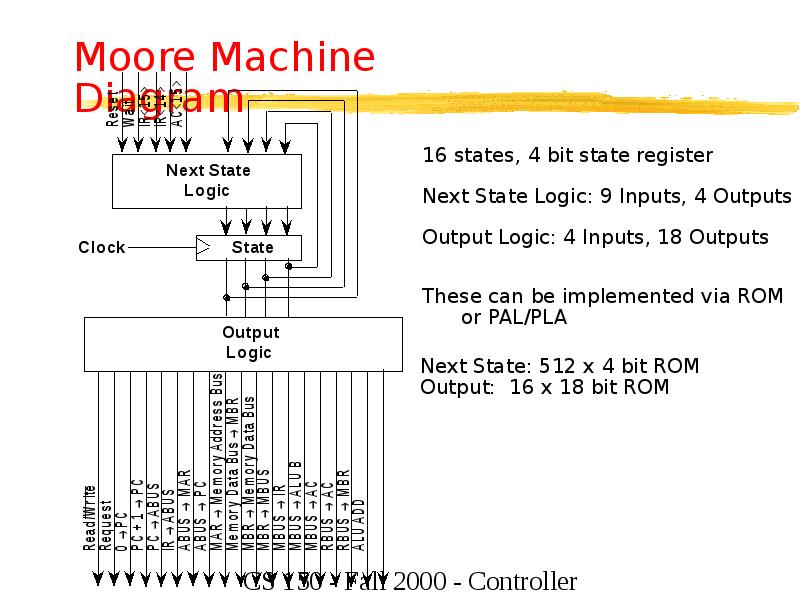

- 6. Moore Machine Diagram

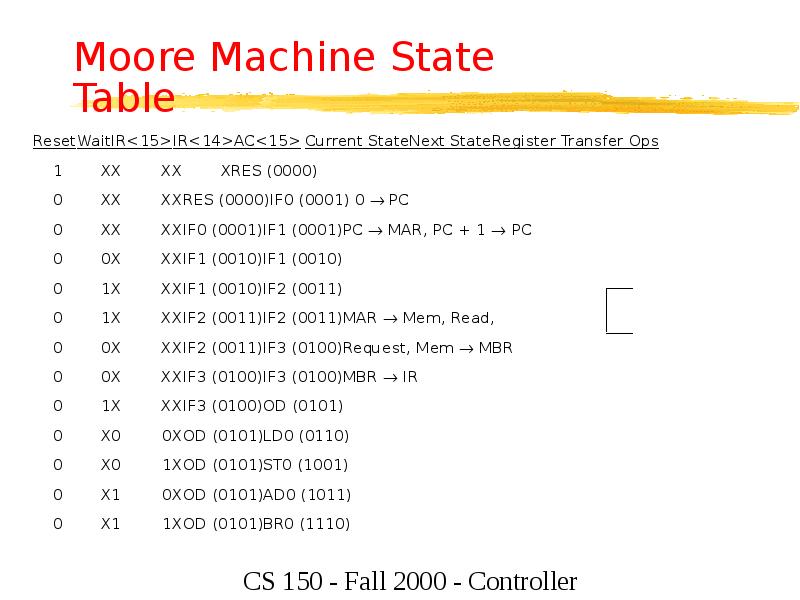

- 7. Moore Machine State Table Reset Wait IR<15> IR<14> AC<15> Current State Next State Register Transfer Ops 1 X X X X X RES (0000)

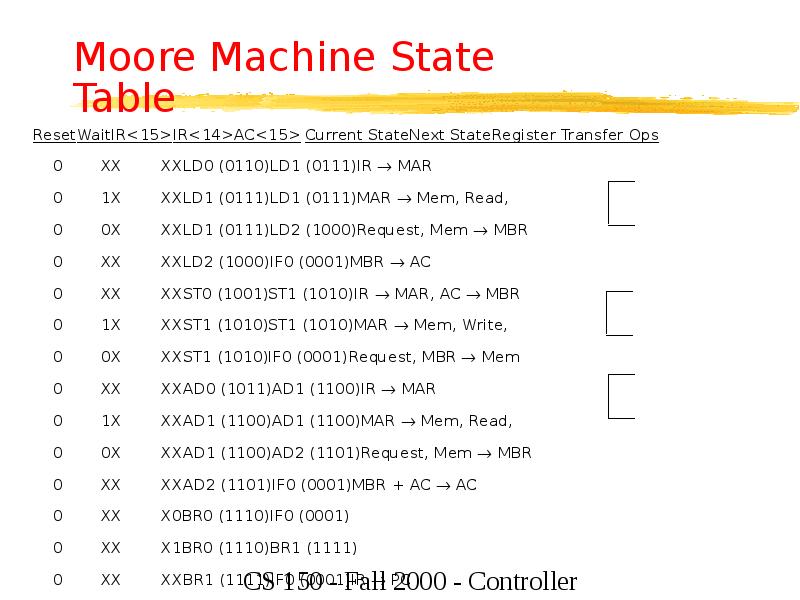

- 8. Moore Machine State Table Reset Wait IR<15> IR<14> AC<15> Current State Next State Register Transfer Ops 0 X X X X LD0 (0110) LD1

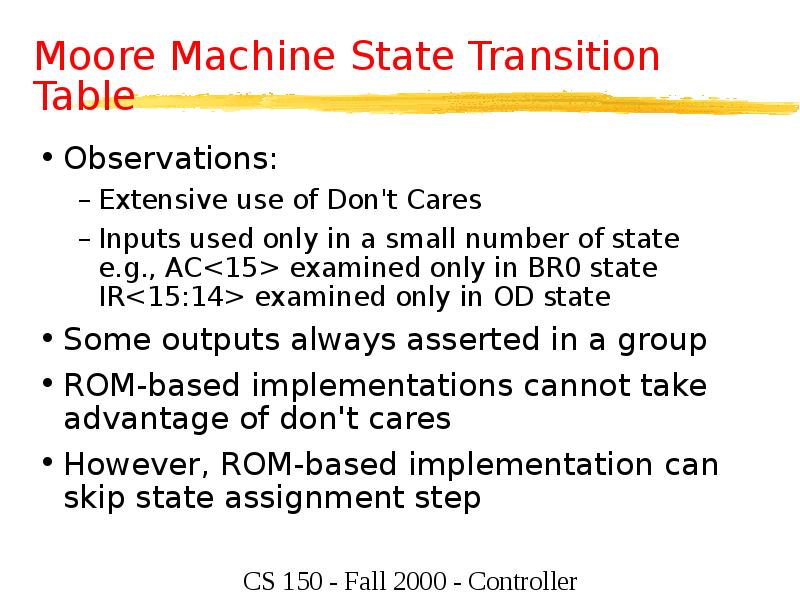

- 9. Moore Machine State Transition Table Observations: Extensive use of Don't Cares

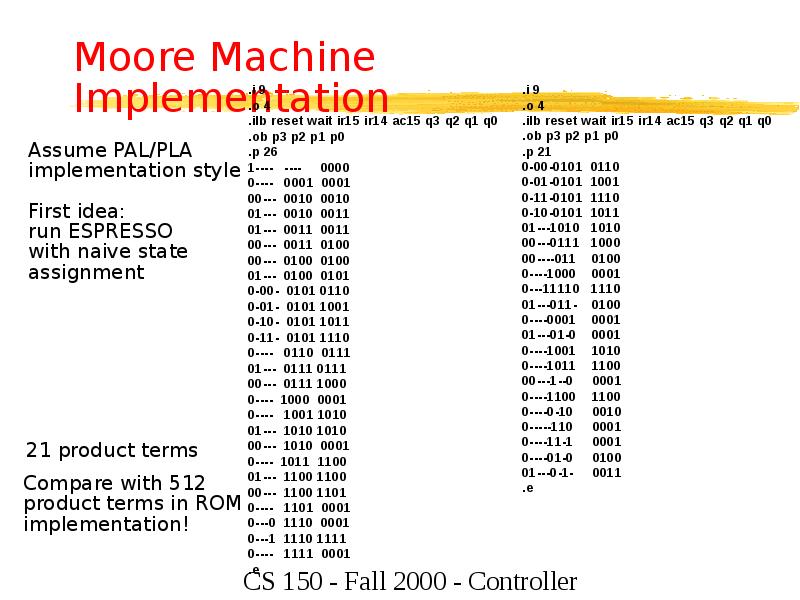

- 10. Moore Machine Implementation

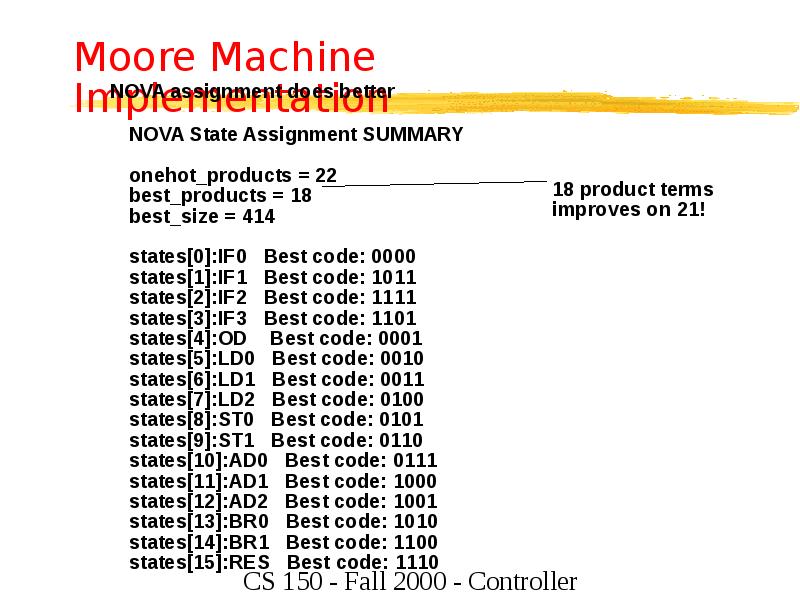

- 11. Moore Machine Implementation

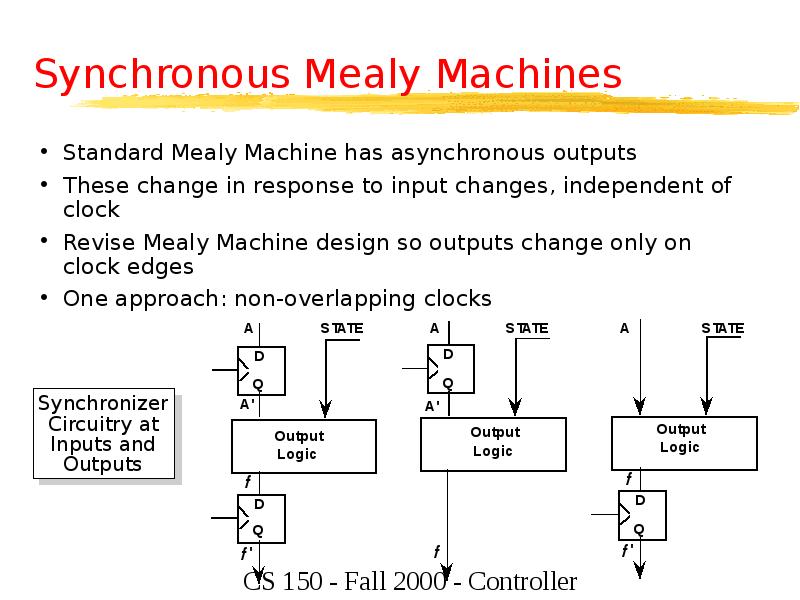

- 12. Synchronous Mealy Machines Standard Mealy Machine has asynchronous outputs These change

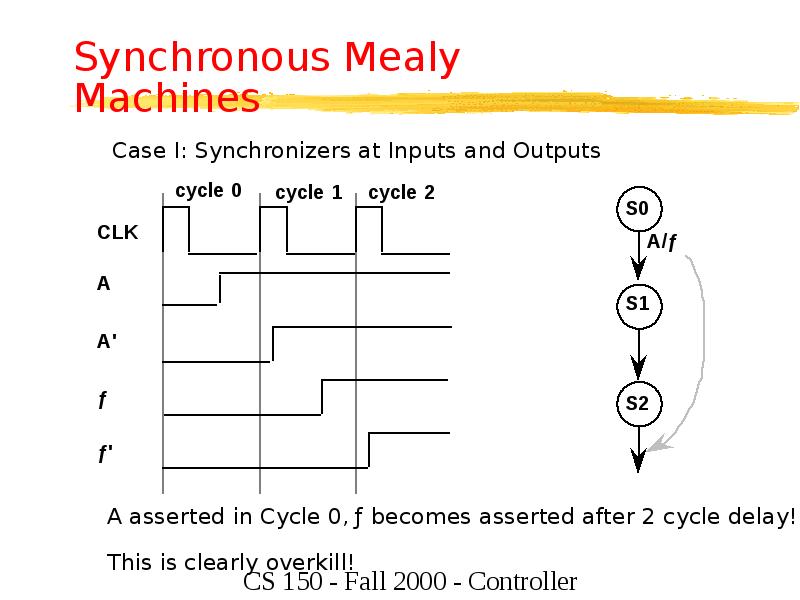

- 13. Synchronous Mealy Machines

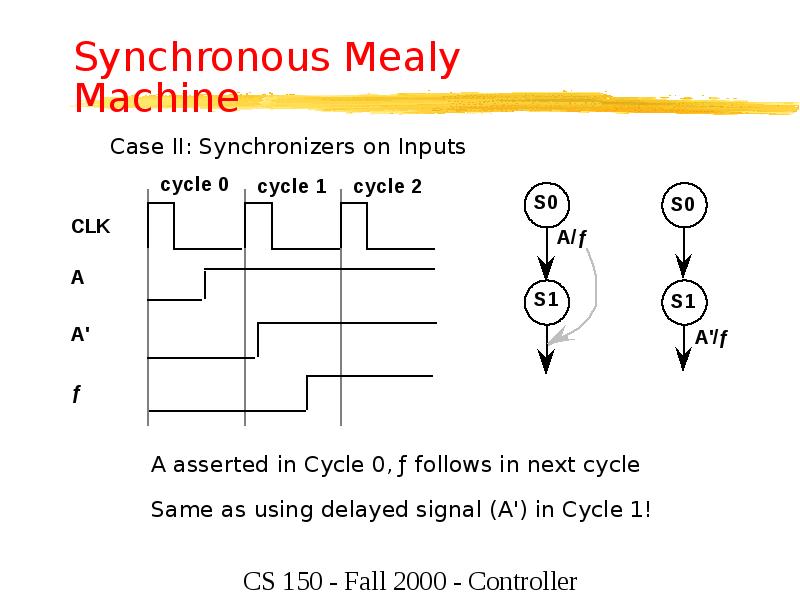

- 14. Synchronous Mealy Machine

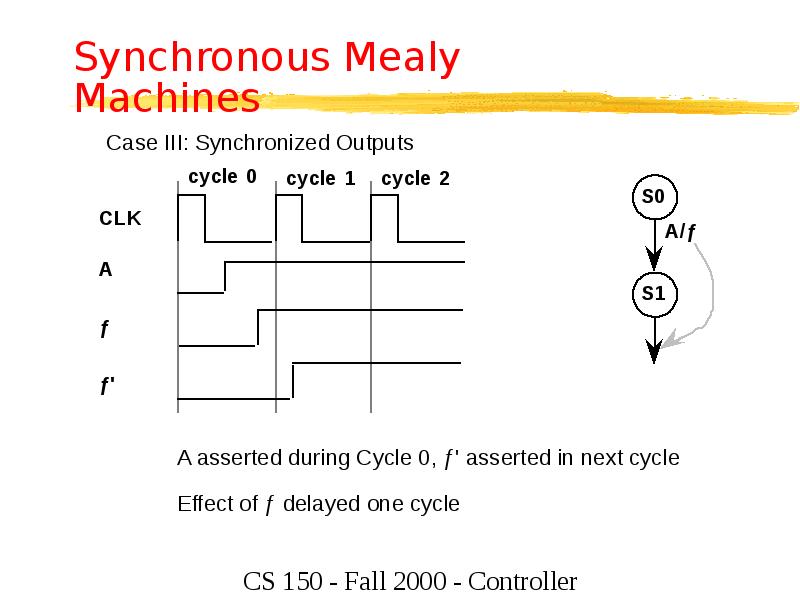

- 15. Synchronous Mealy Machines

- 16. Synchronous Mealy Machines Implications for Processor FSM Already Derived Consider inputs:

- 17. Time State Divide and Conquer Overview Classical Approach: Monolithic Implementations Alternative

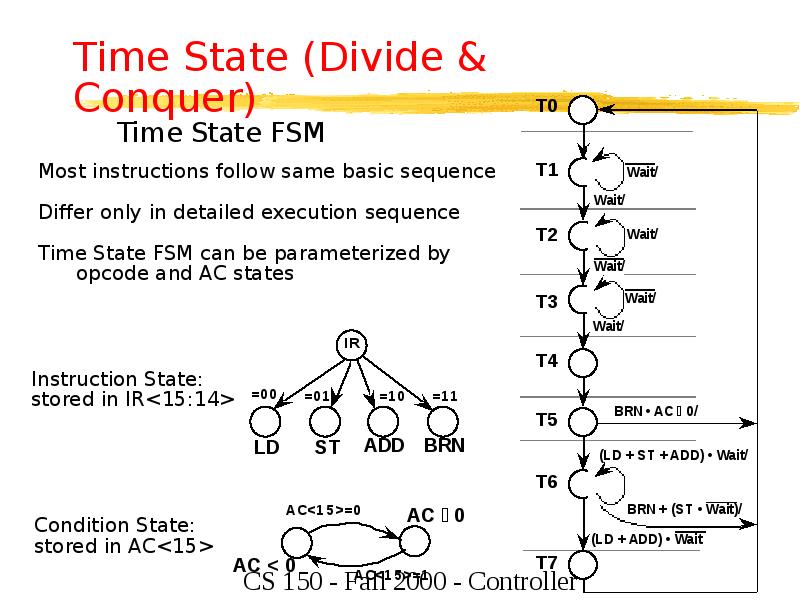

- 18. Time State (Divide & Conquer)

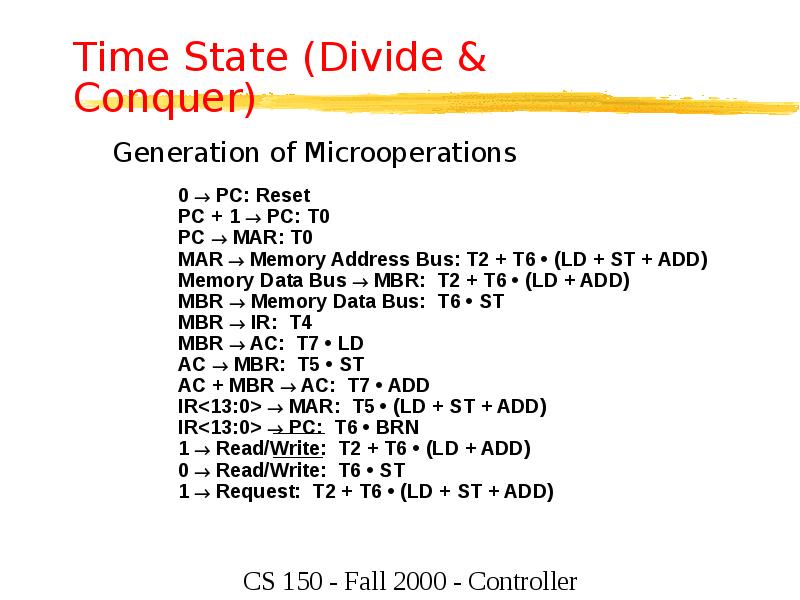

- 19. Time State (Divide & Conquer)

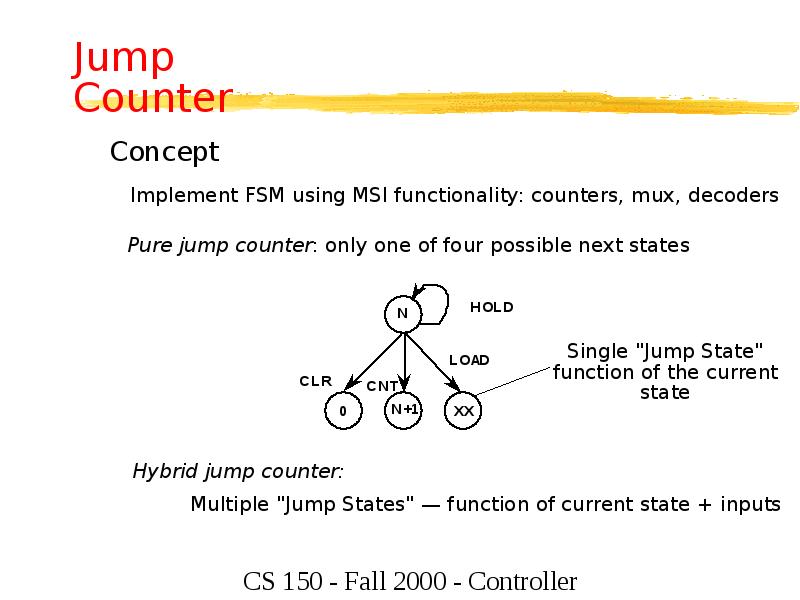

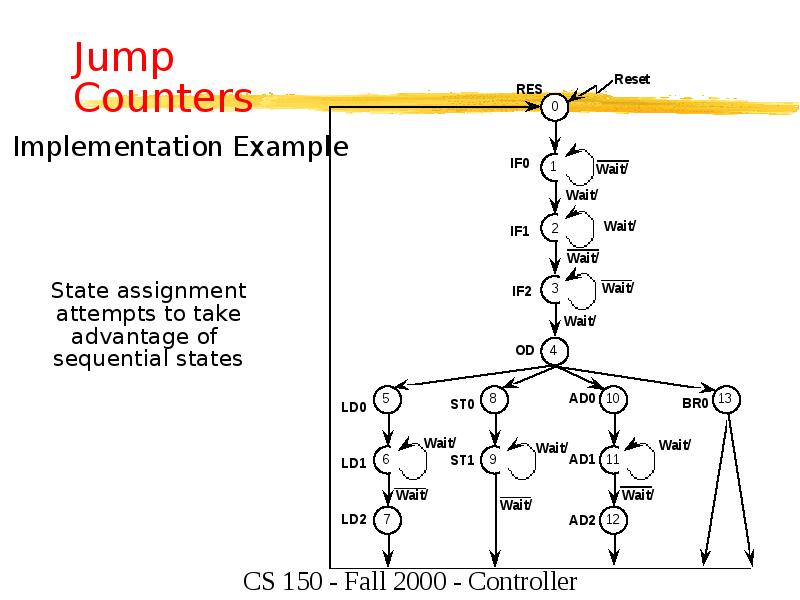

- 20. Jump Counter

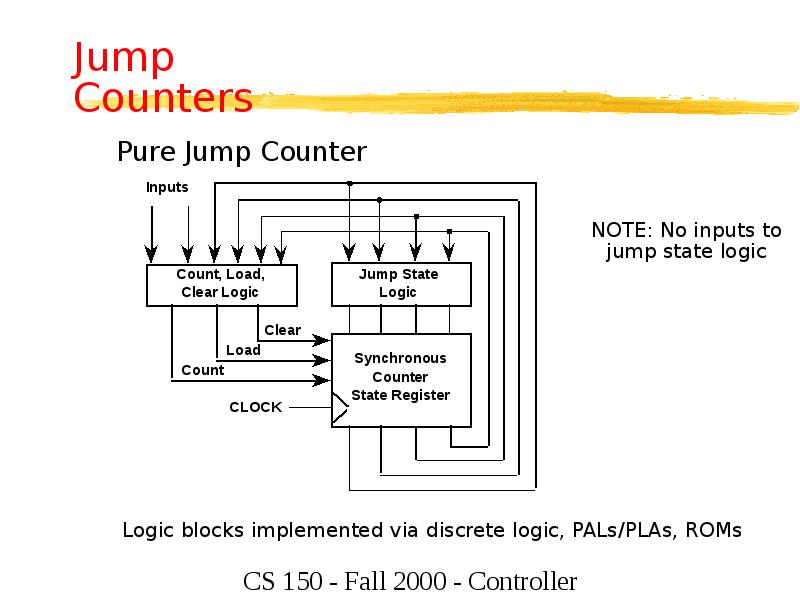

- 21. Jump Counters

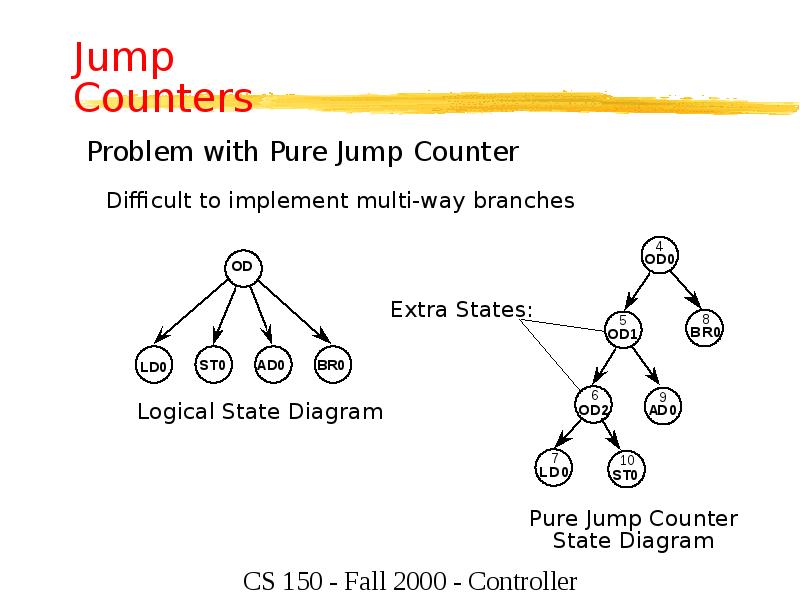

- 22. Jump Counters

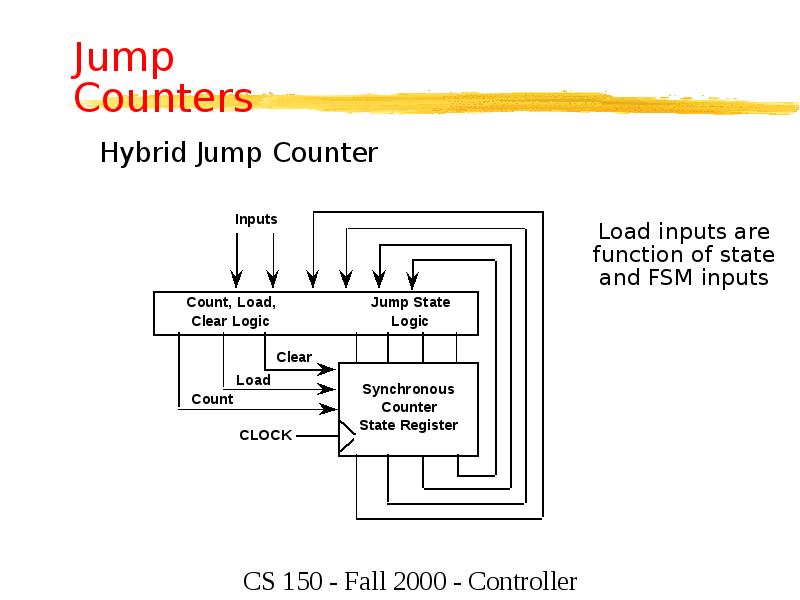

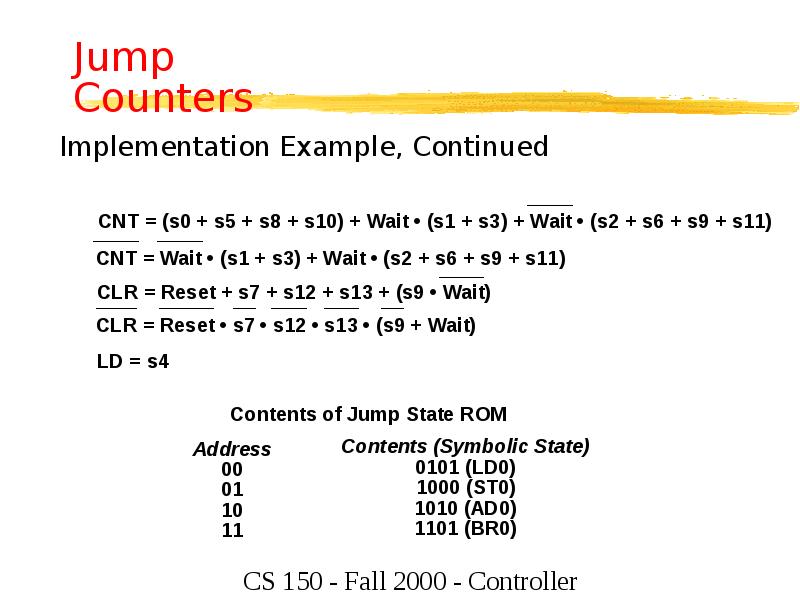

- 23. Jump Counters

- 24. Jump Counters

- 25. Jump Counters

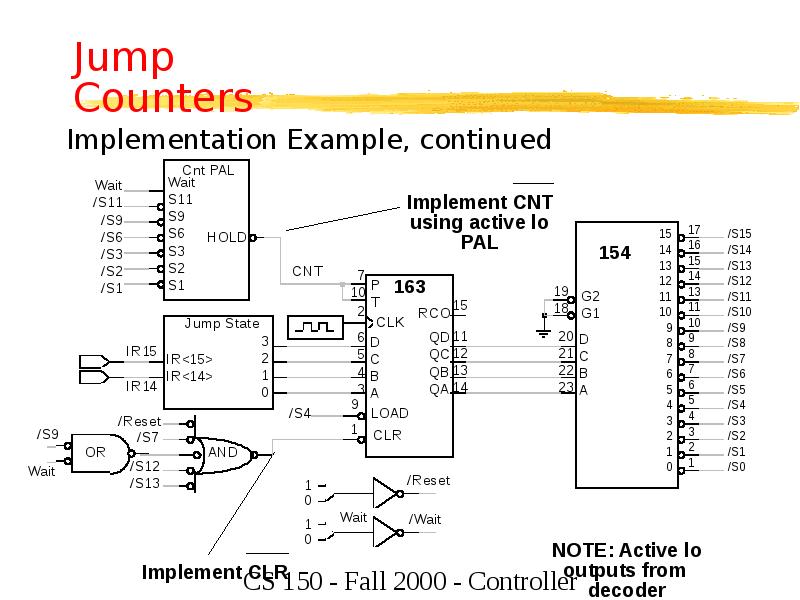

- 26. Jump Counters

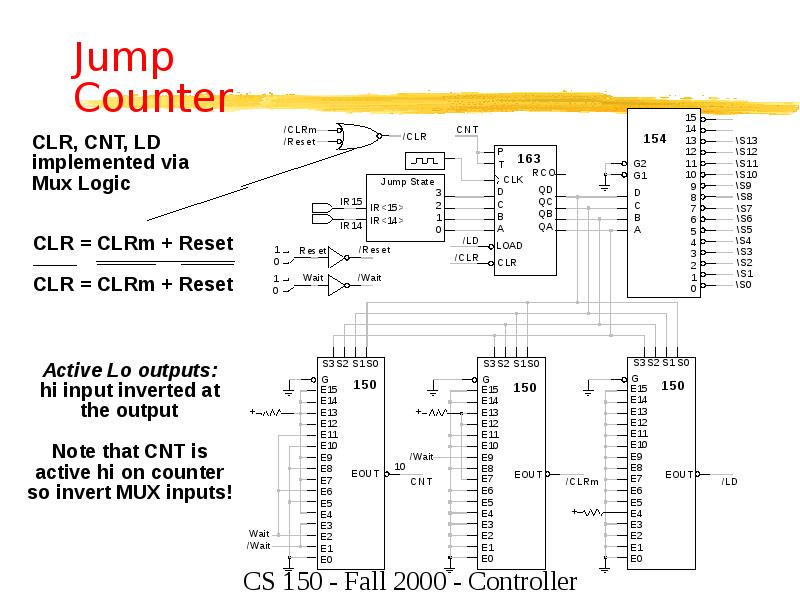

- 27. Jump Counter

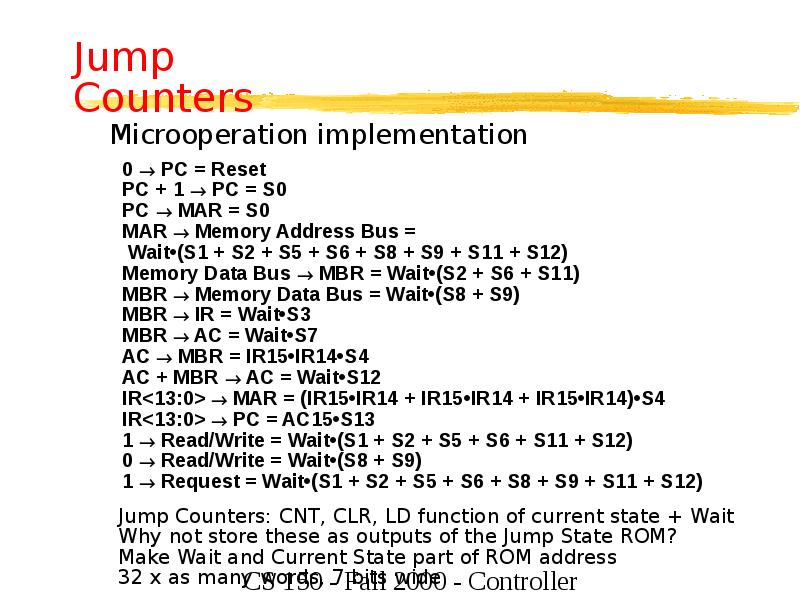

- 28. Jump Counters

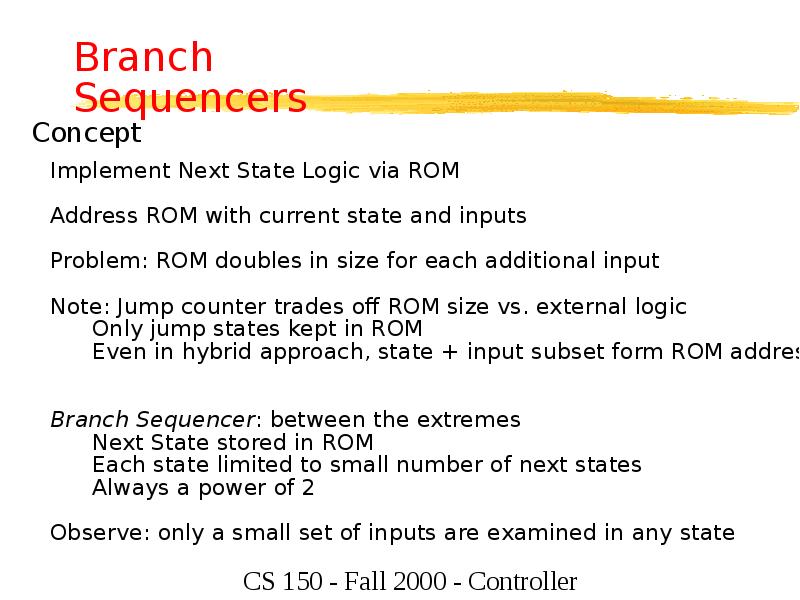

- 29. Branch Sequencers

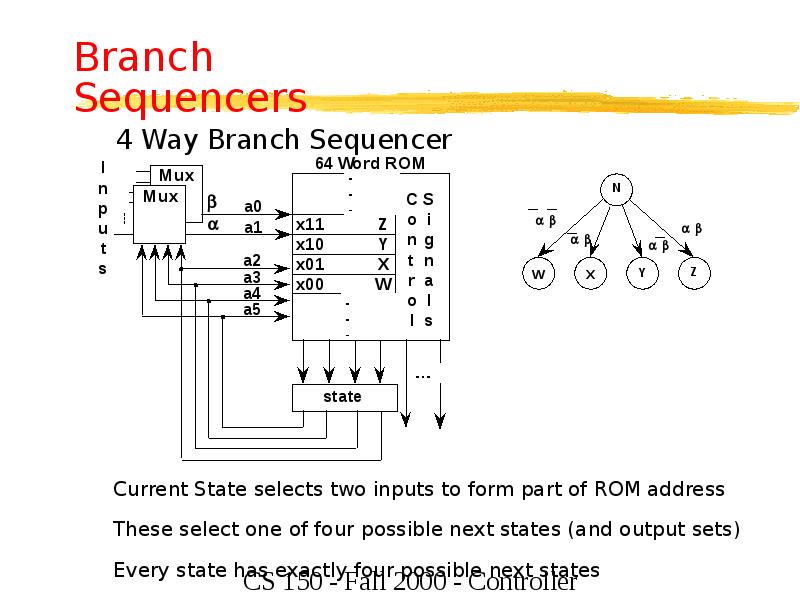

- 30. Branch Sequencers

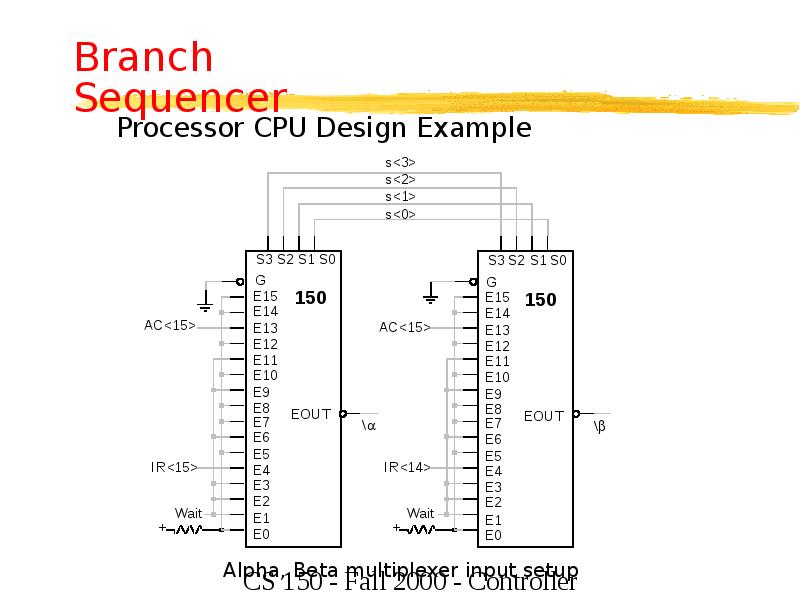

- 31. Branch Sequencer

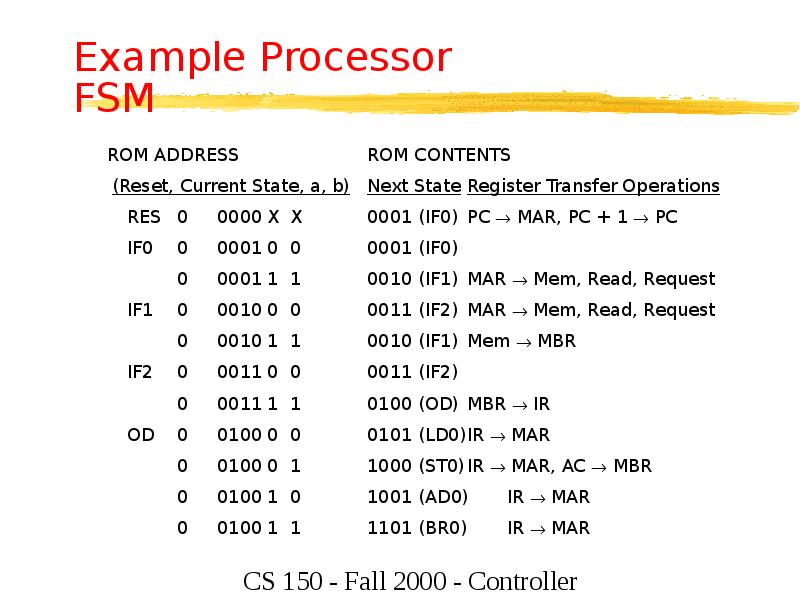

- 32. Example Processor FSM ROM ADDRESS ROM CONTENTS (Reset, Current State, a, b) Next

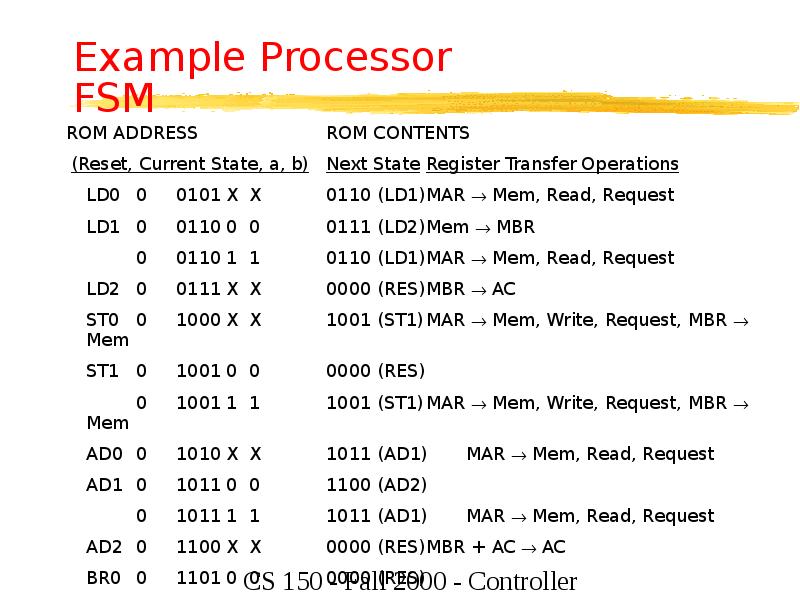

- 33. Example Processor FSM ROM ADDRESS ROM CONTENTS (Reset, Current State, a, b) Next

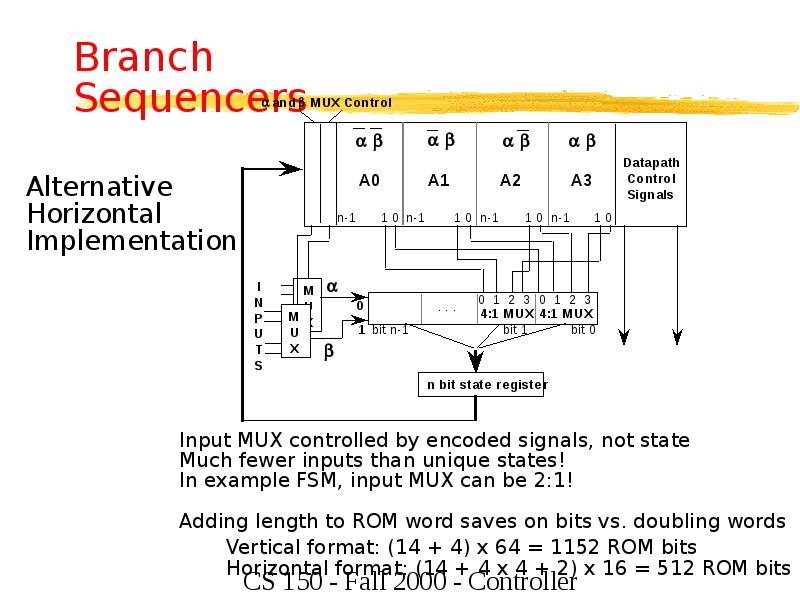

- 34. Branch Sequencers

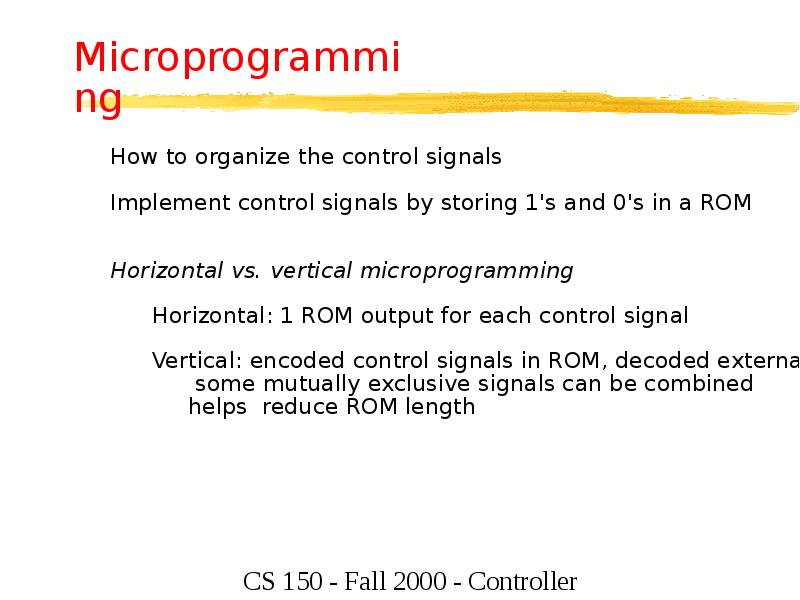

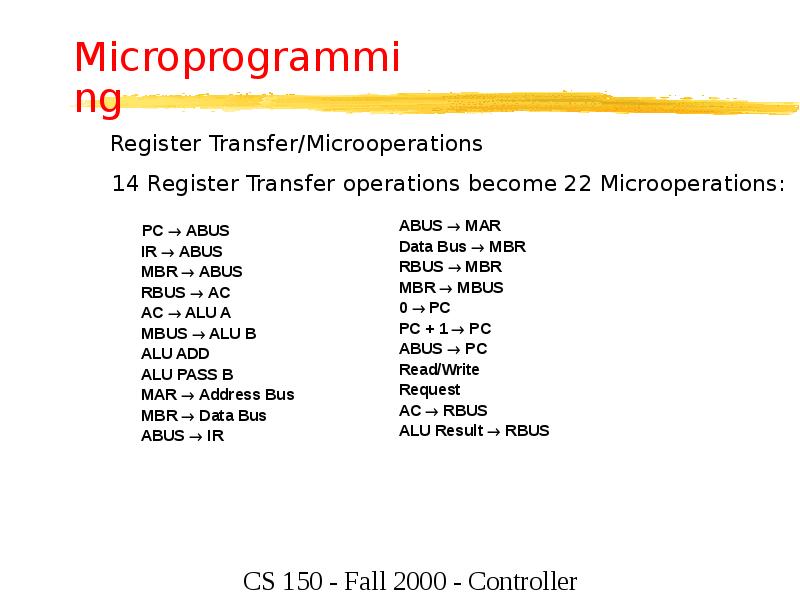

- 35. Microprogramming

- 36. Microprogramming

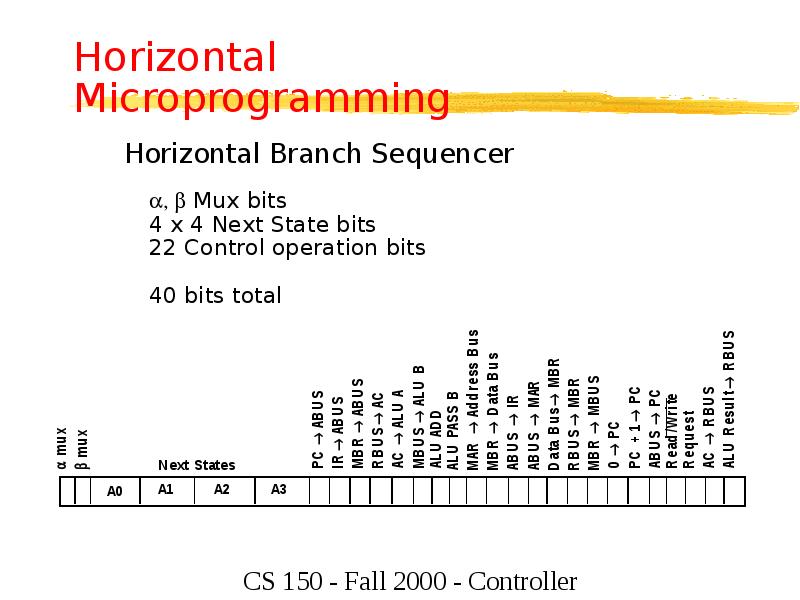

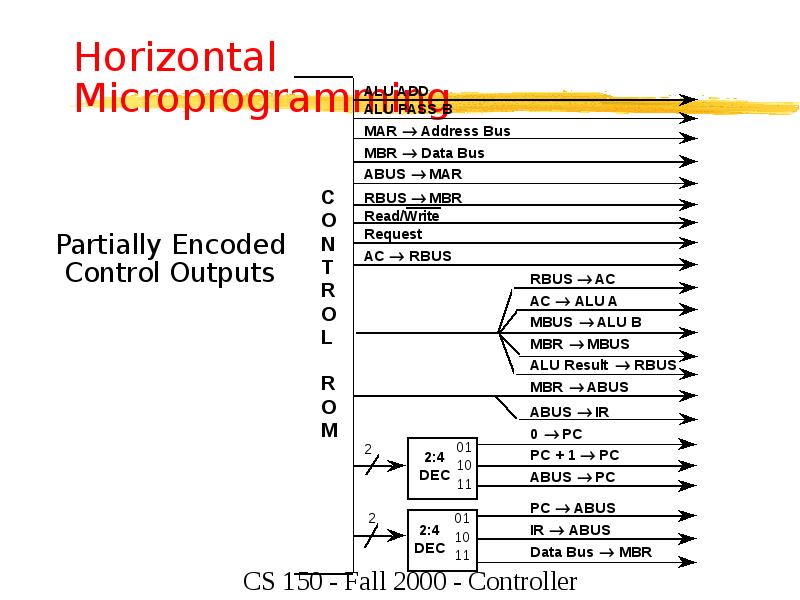

- 37. Horizontal Microprogramming

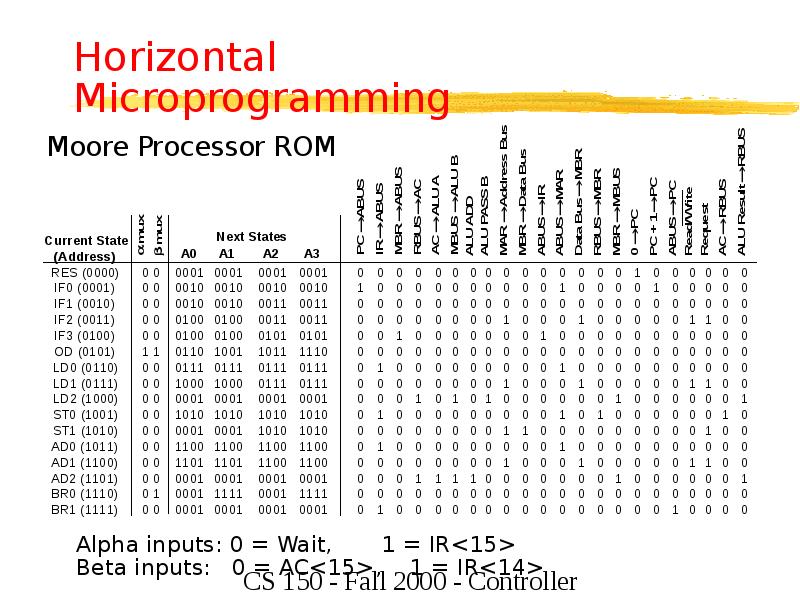

- 38. Horizontal Microprogramming

- 39. Horizontal Microprogramming

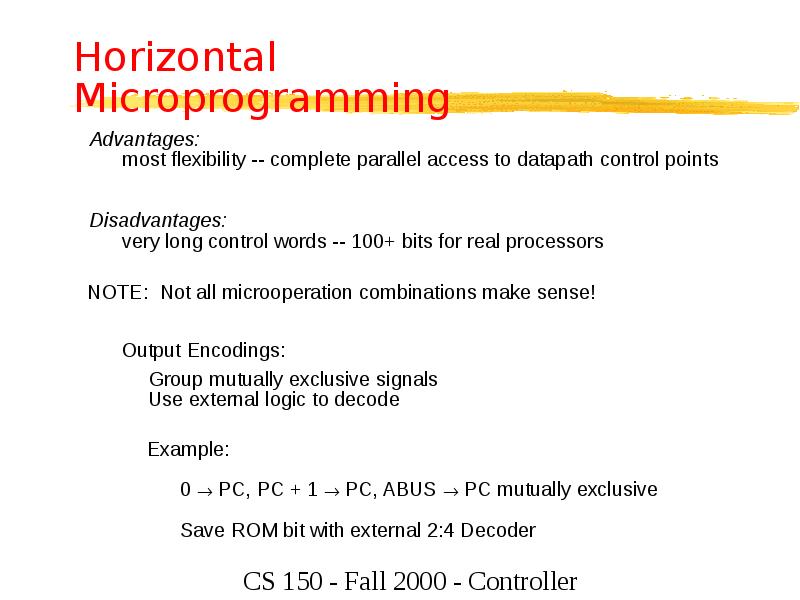

- 40. Horizontal Microprogramming

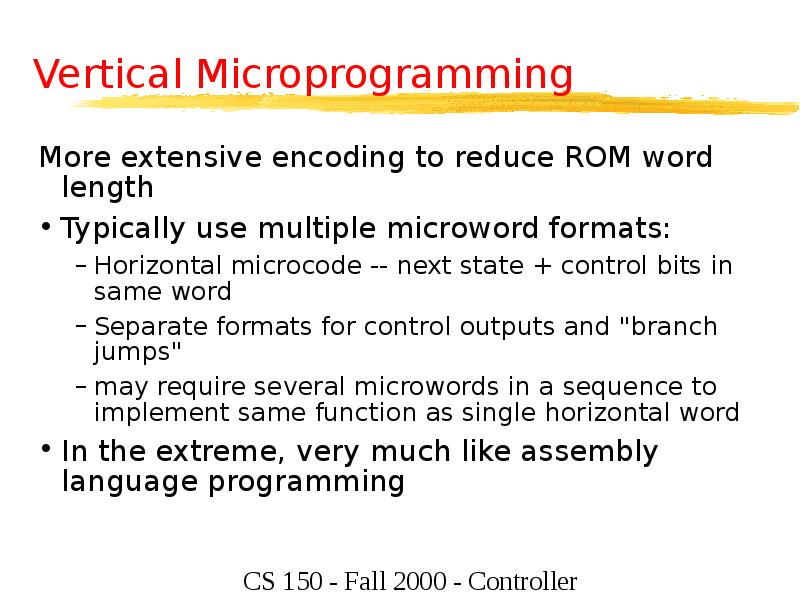

- 41. Vertical Microprogramming More extensive encoding to reduce ROM word length Typically

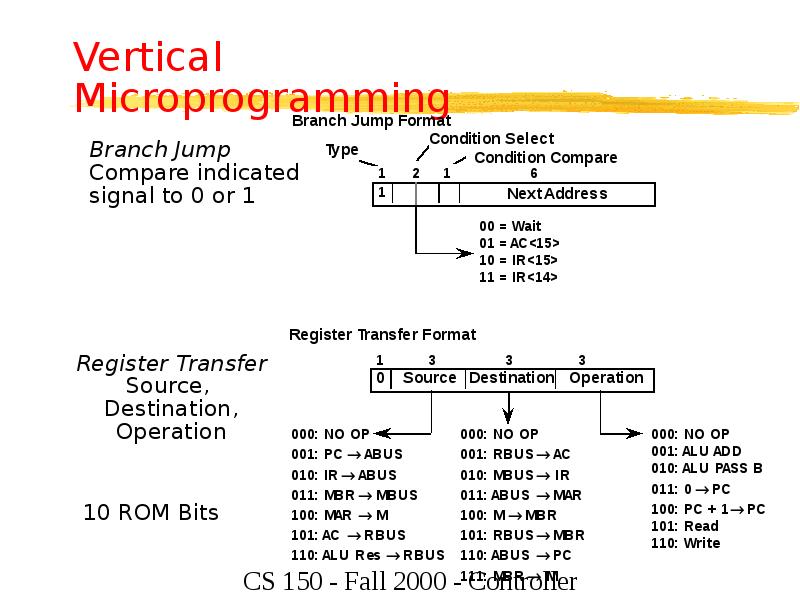

- 42. Vertical Microprogramming

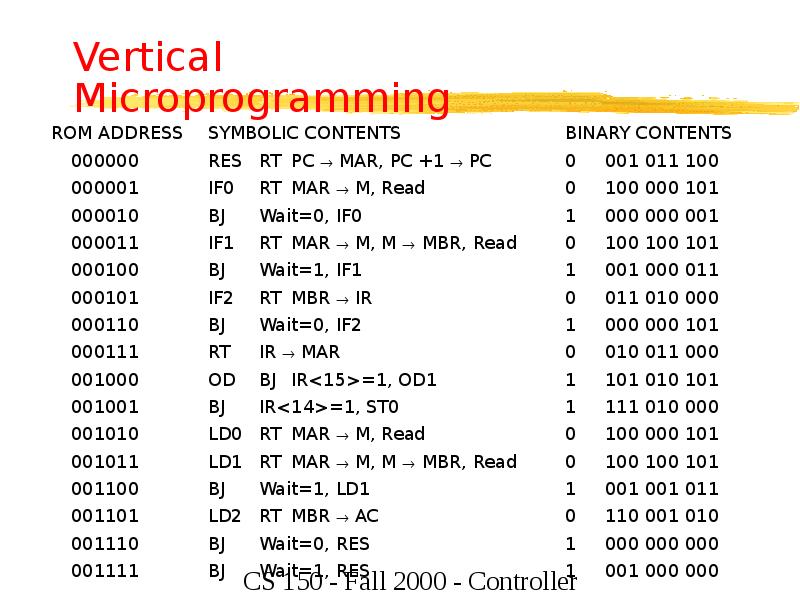

- 43. Vertical Microprogramming ROM ADDRESS SYMBOLIC CONTENTS BINARY CONTENTS 000000 RES RT PC MAR, PC +1

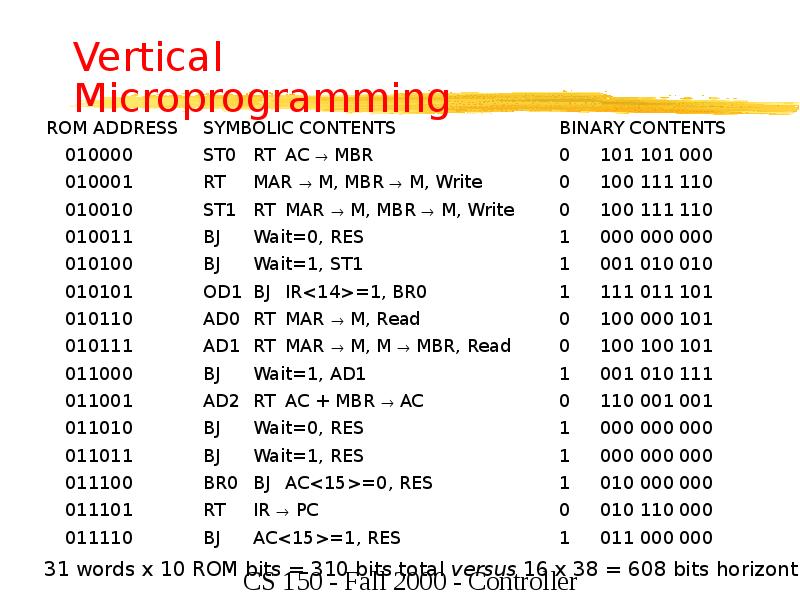

- 44. Vertical Microprogramming ROM ADDRESS SYMBOLIC CONTENTS BINARY CONTENTS 010000 ST0 RT AC MBR 0 101 101 000 010001 RT MAR

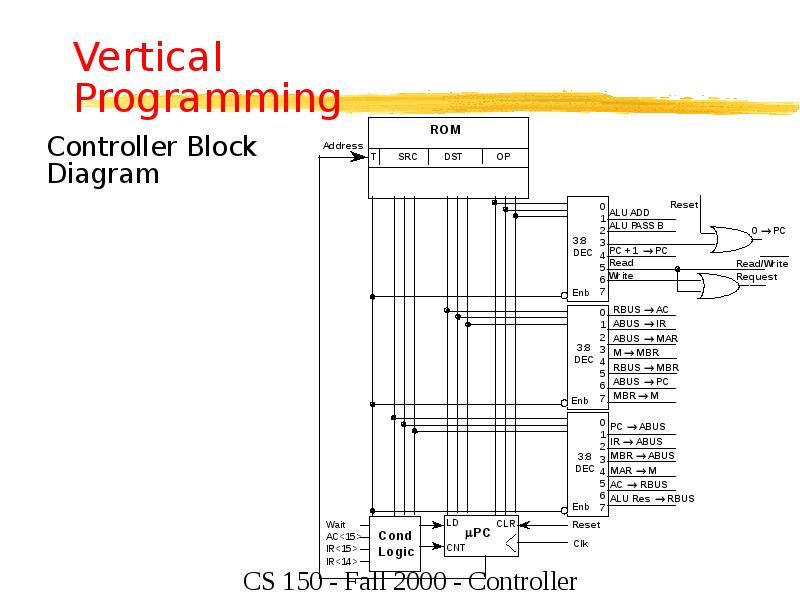

- 45. Vertical Programming

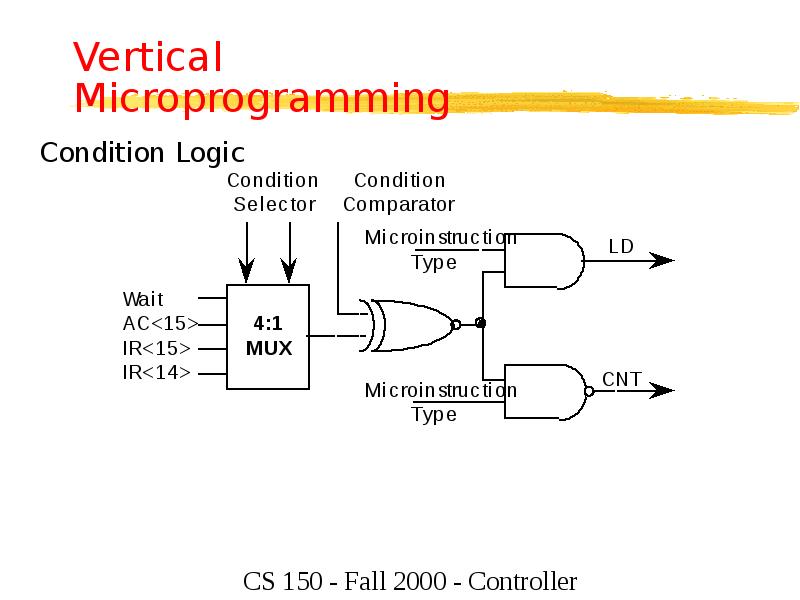

- 46. Vertical Microprogramming

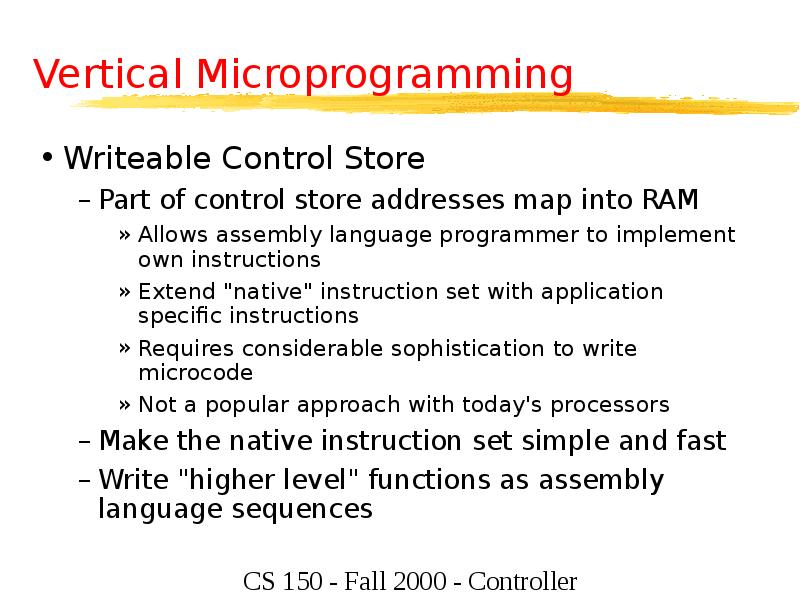

- 47. Vertical Microprogramming Writeable Control Store Part of control store addresses map

- 48. Controller Implementation Summary Control Unit Organization Register transfer operation Classical Moore

- 49. Скачать презентацию

Слайды и текст этой презентации

Похожие презентации