Архитектура фон Неймана и Гарварда презентация презентация

Содержание

- 2. В 1946 году Д. фон Нейман, Г. Голдстайн и А. Беркс

- 3. 1. Использование двоичной системы счисления в вычислительных машинах. Преимущество перед десятичной

- 4. 2. Программное управление ЭВМ Работа ЭВМ контролируется программой, состоящей из набора

- 5. 3. Память компьютера используется не только для хранения данных, но и

- 6. 4. Ячейки памяти ЭВМ имеют адреса, которые последовательно пронумерованы В любой

- 7. 5. Возможность условного перехода в процессе выполнения программы. Не смотря на

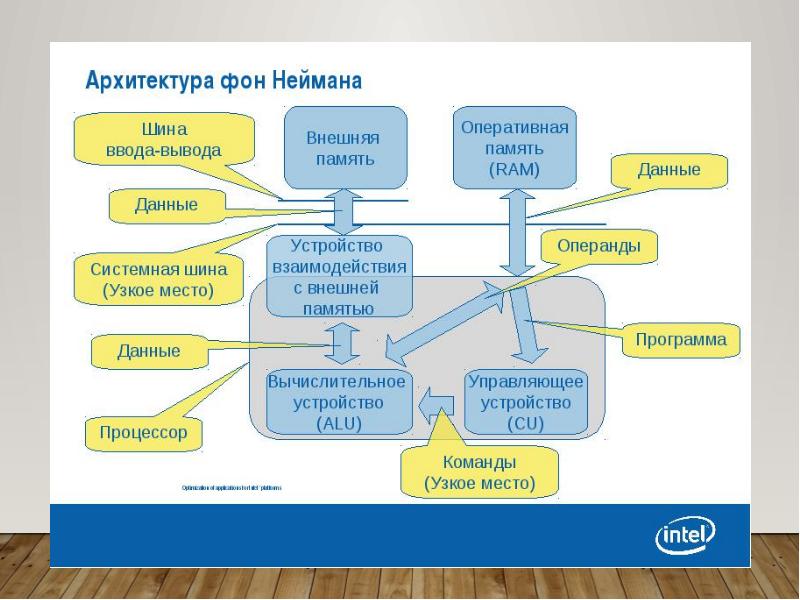

- 8. Архитектура фон Неймана

- 10. Поколения компьютеров - история развития вычислительной техники

- 11. Нулевое поколение. Механические вычислители счетная машина блеза паскаля, 1642 г. эта

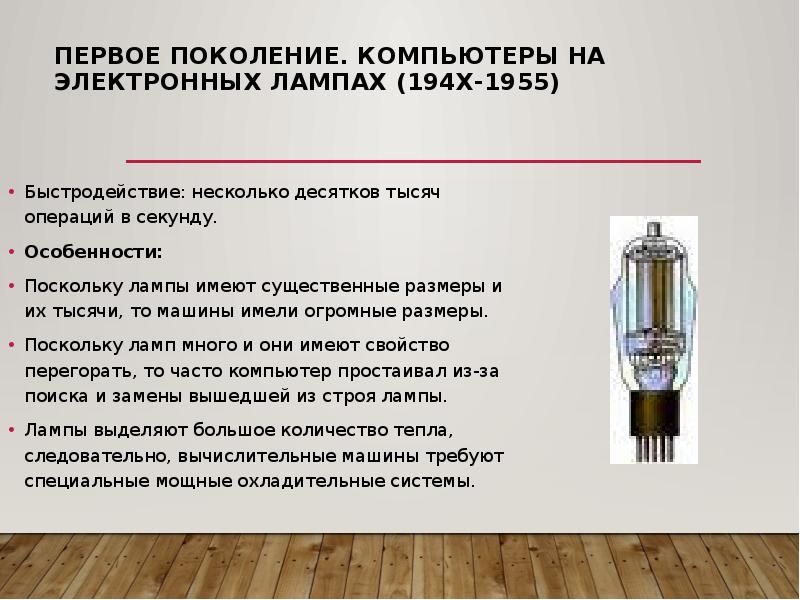

- 12. Первое поколение. Компьютеры на электронных лампах (194х-1955) Быстродействие: несколько десятков

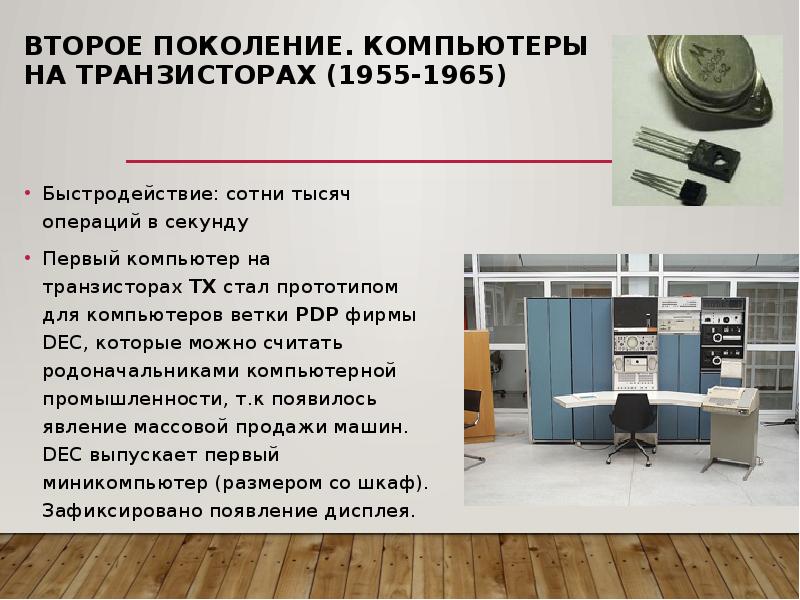

- 14. Второе поколение. Компьютеры на транзисторах (1955-1965) Быстродействие: сотни тысяч операций

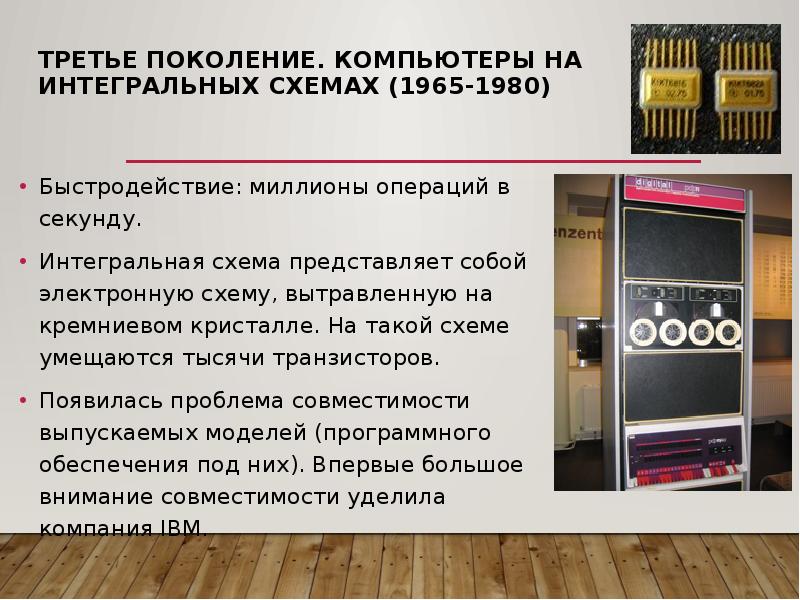

- 15. Третье поколение. Компьютеры на интегральных схемах (1965-1980) Быстродействие: миллионы операций

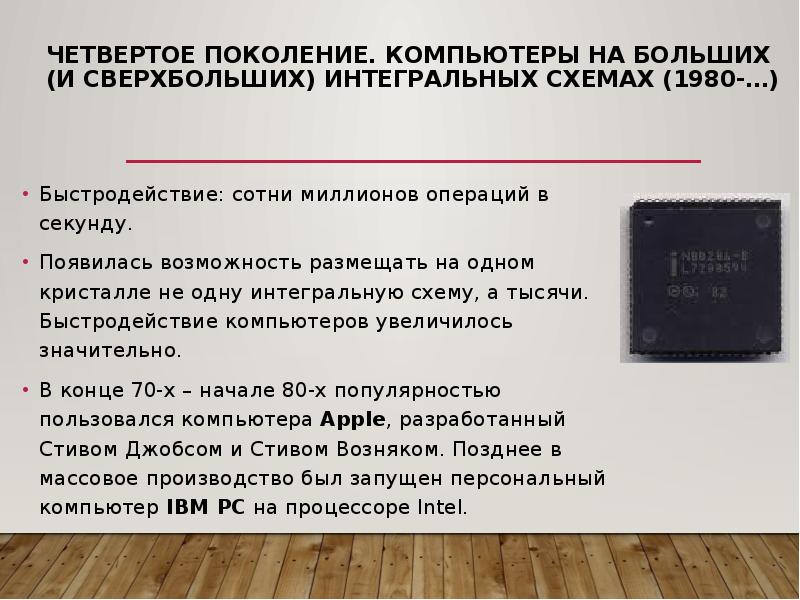

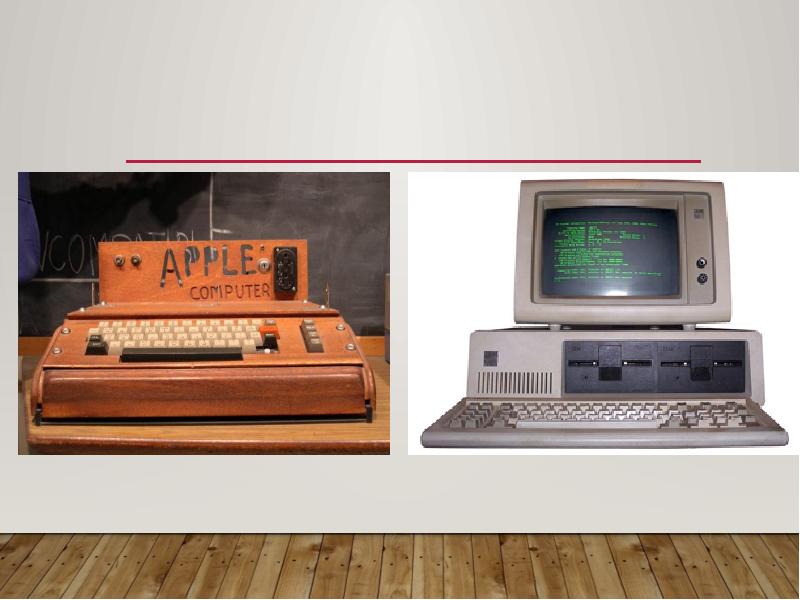

- 16. Четвертое поколение. Компьютеры на больших (и сверхбольших) интегральных схемах (1980-…)

- 18. Пятое поколение?

- 19. Характеристики шестого поколения

- 20. Гарвардская архитектура и её достоинства При реализации микропроцессоров традиционно используется

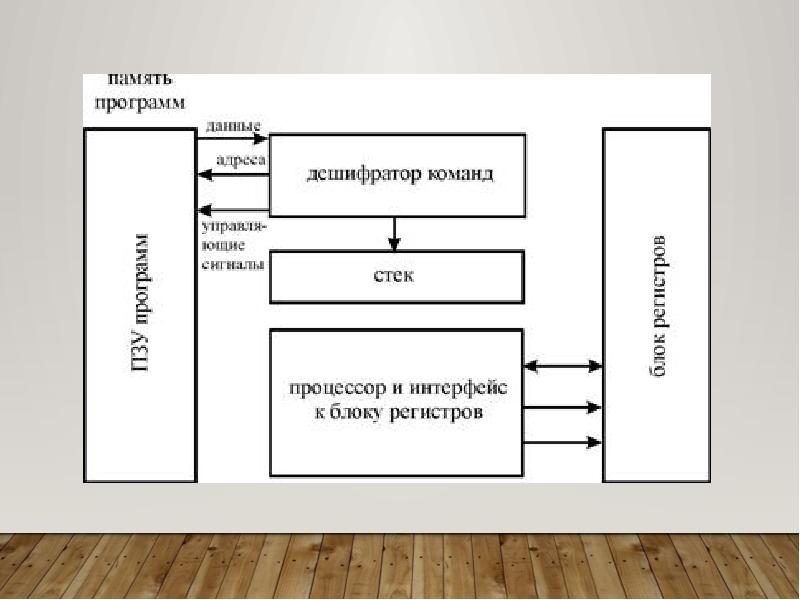

- 21. В качестве недостатка архитектуры фон Неймана можно назвать возможность непреднамеренного нарушения

- 23. Эти особенности определили области применения гарвардской архитектуры. Гарвардская архитектура применяется в

- 24. В Гарвардской архитектуре характеристики устройств памяти программ и памяти данных не

- 25. Применение двух системных шин для обращения к памяти программ и памяти

- 26. В сигнальных процессорах для реализации таких алгоритмах как быстрое преобразование Фурье и цифровая

- 27. Скачать презентацию

Слайды и текст этой презентации

Скачать презентацию на тему Архитектура фон Неймана и Гарварда презентация можно ниже:

Похожие презентации