Память в вычислительных системах презентация

Содержание

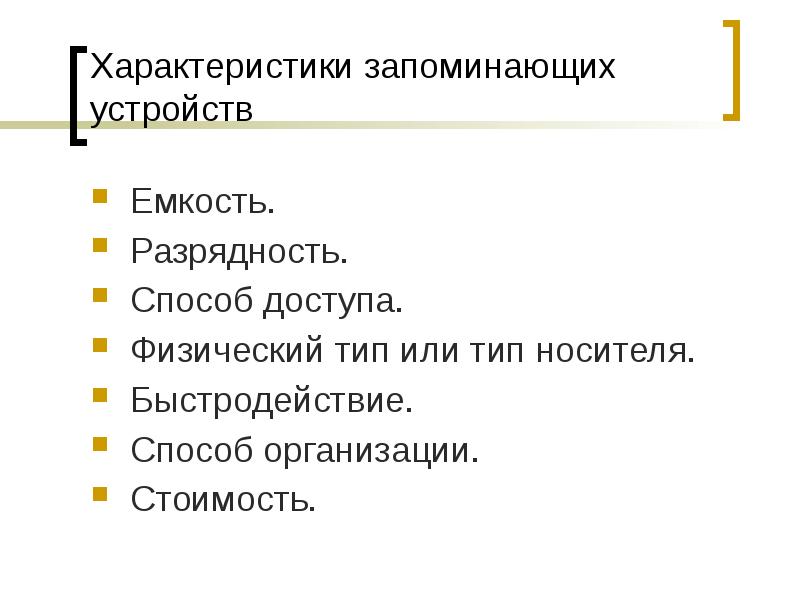

- 2. Характеристики запоминающих устройств Емкость. Разрядность. Способ доступа. Физический тип или тип

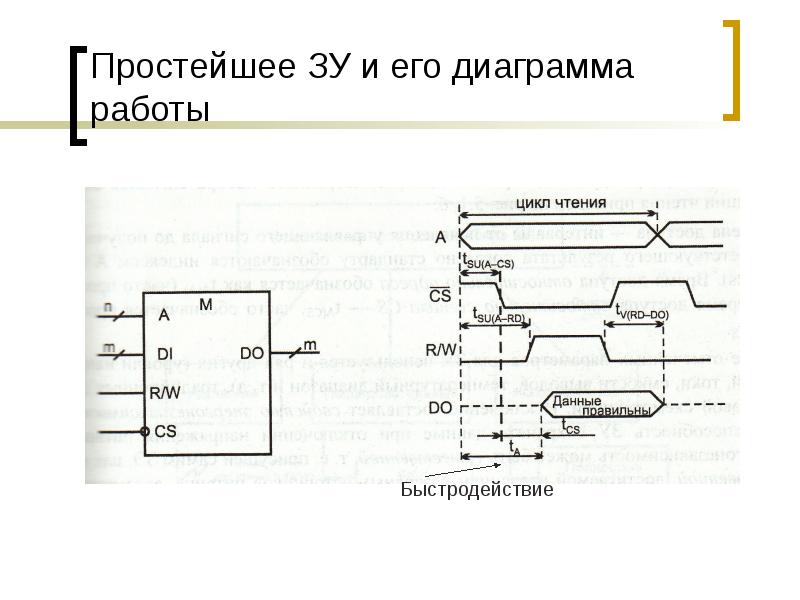

- 3. Простейшее ЗУ и его диаграмма работы

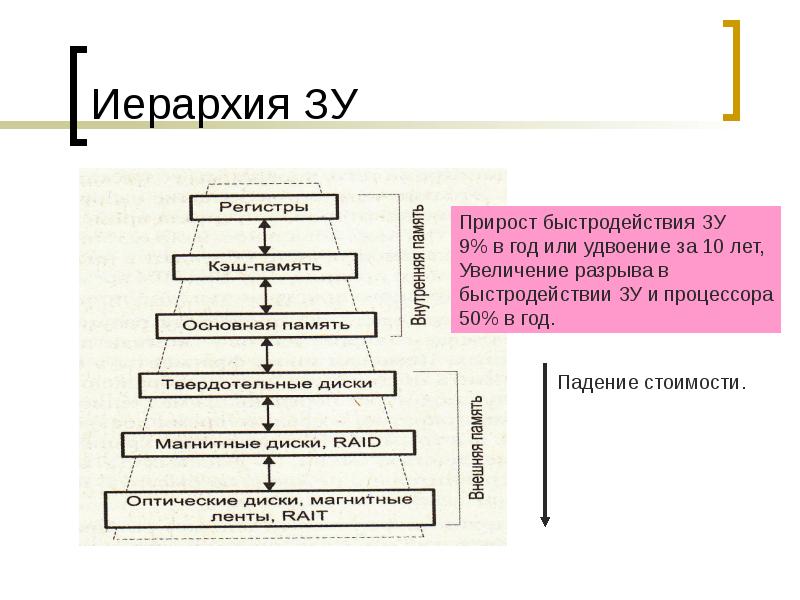

- 4. Иерархия ЗУ

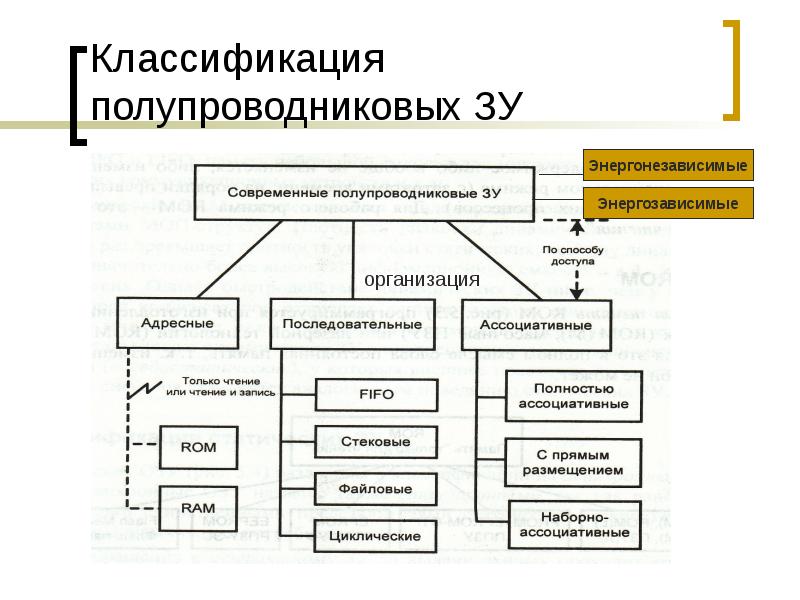

- 5. Классификация полупроводниковых ЗУ

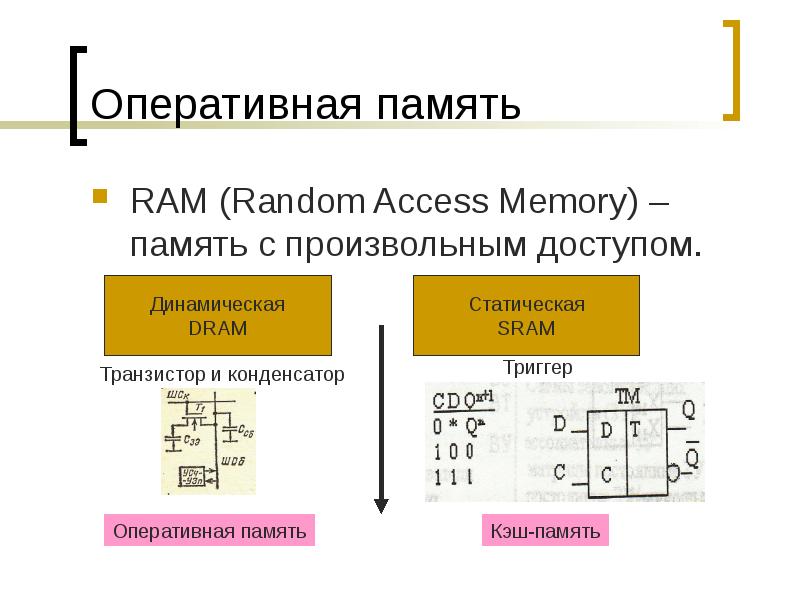

- 6. Оперативная память RAM (Random Access Memory) – память с произвольным доступом.

- 7. SRAM

- 8. Способы организации ЗУ Структура 2D; Структура 3D; Структура 2DM; Блочные структуры;

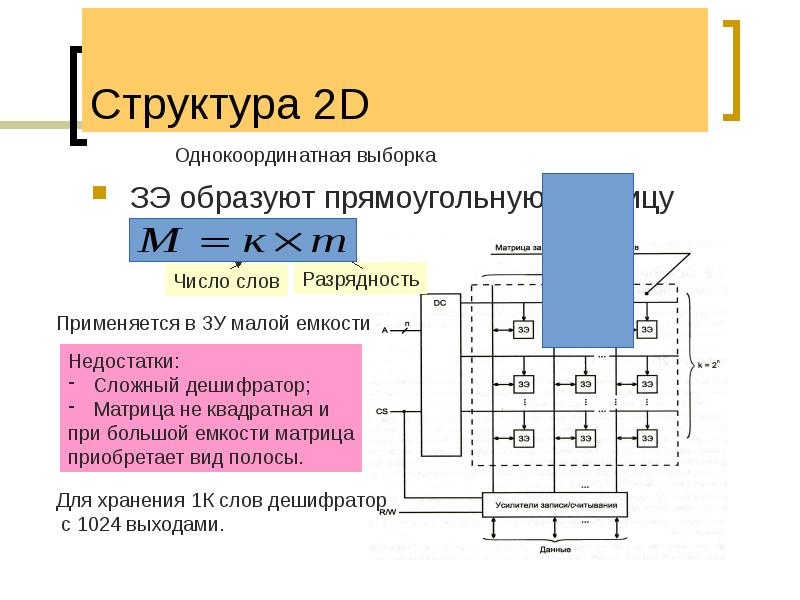

- 9. Структура 2D ЗЭ образуют прямоугольную матрицу

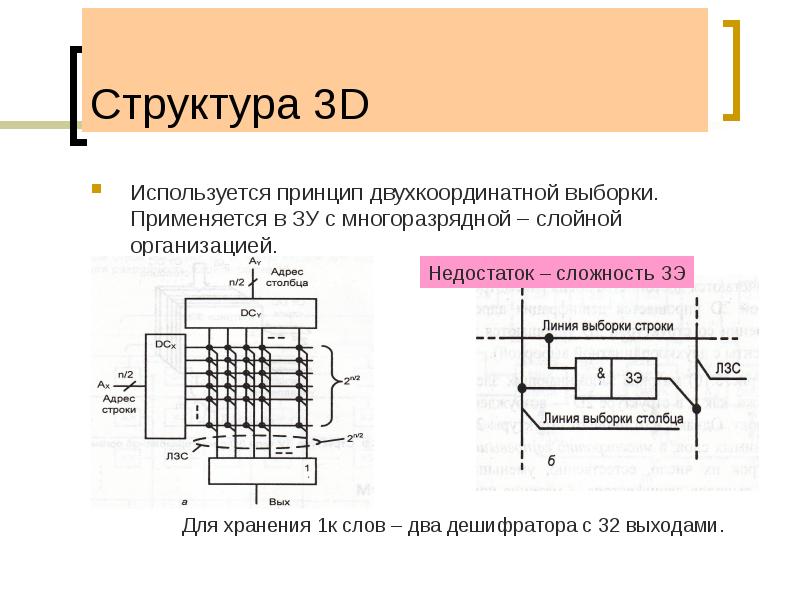

- 10. Структура 3D Используется принцип двухкоординатной выборки. Применяется в ЗУ с многоразрядной

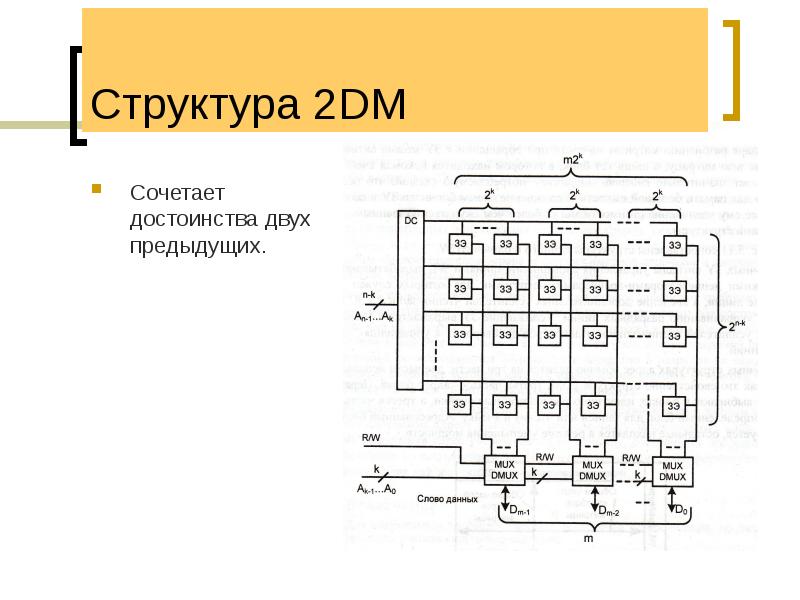

- 11. Структура 2DM Сочетает достоинства двух предыдущих.

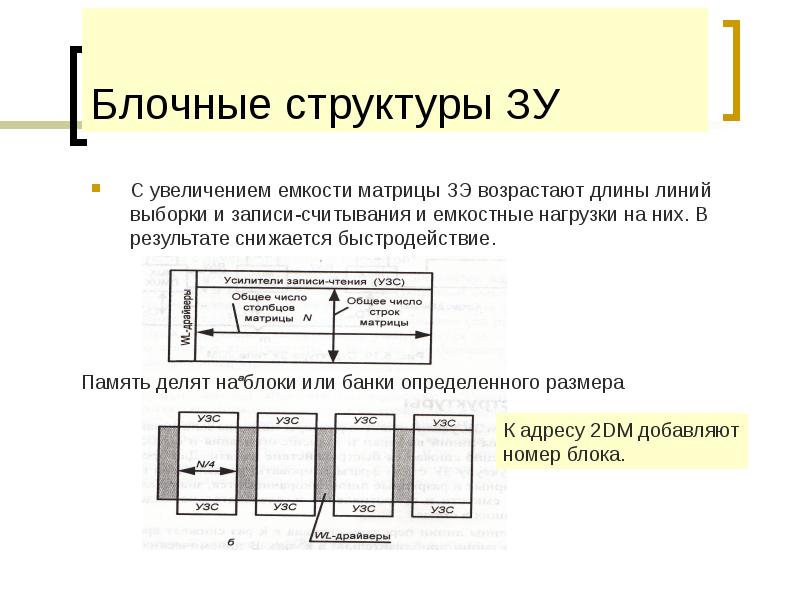

- 12. Блочные структуры ЗУ С увеличением емкости матрицы ЗЭ возрастают длины линий

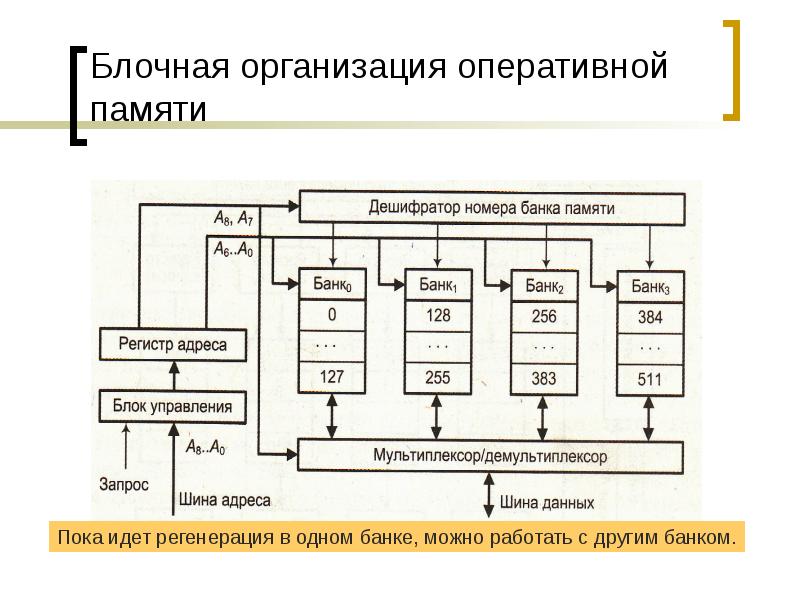

- 13. Блочная организация оперативной памяти

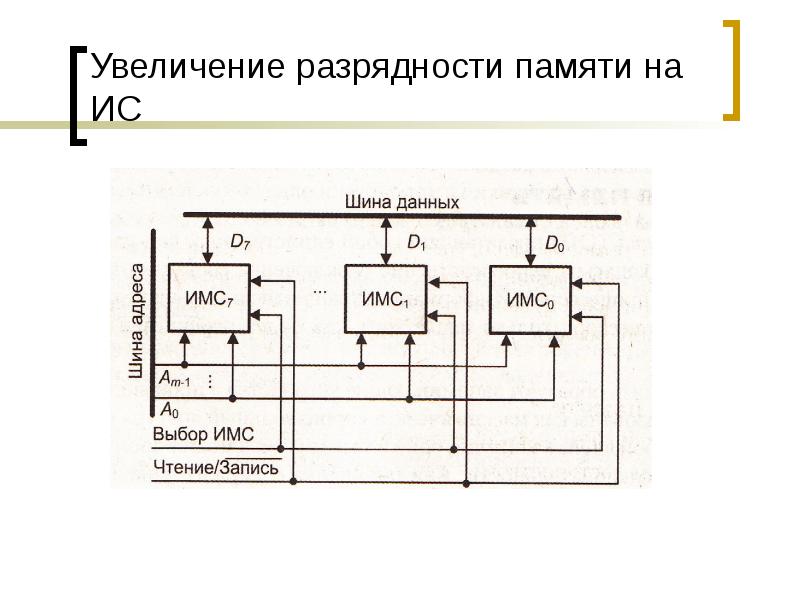

- 14. Увеличение разрядности памяти на ИС

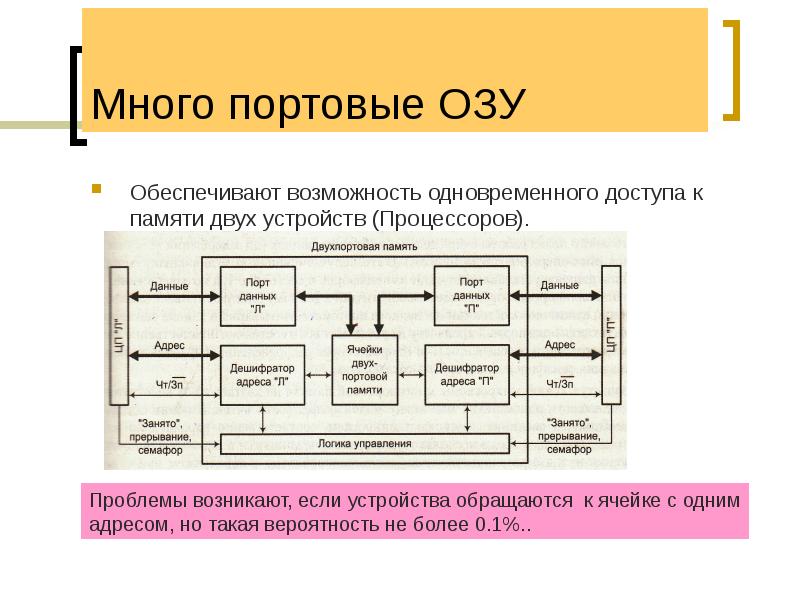

- 15. Много портовые ОЗУ Обеспечивают возможность одновременного доступа к памяти двух устройств

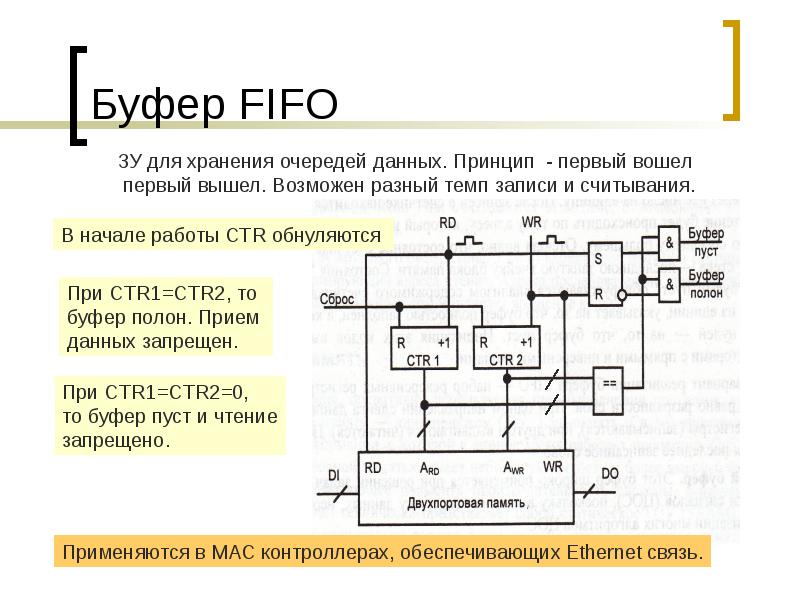

- 16. Буфер FIFO

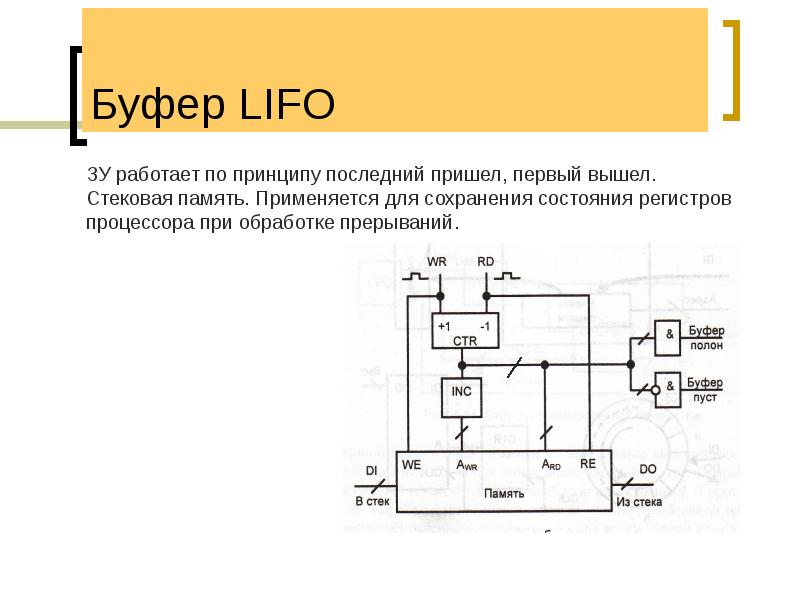

- 17. Буфер LIFO

- 18. Круговой буфер

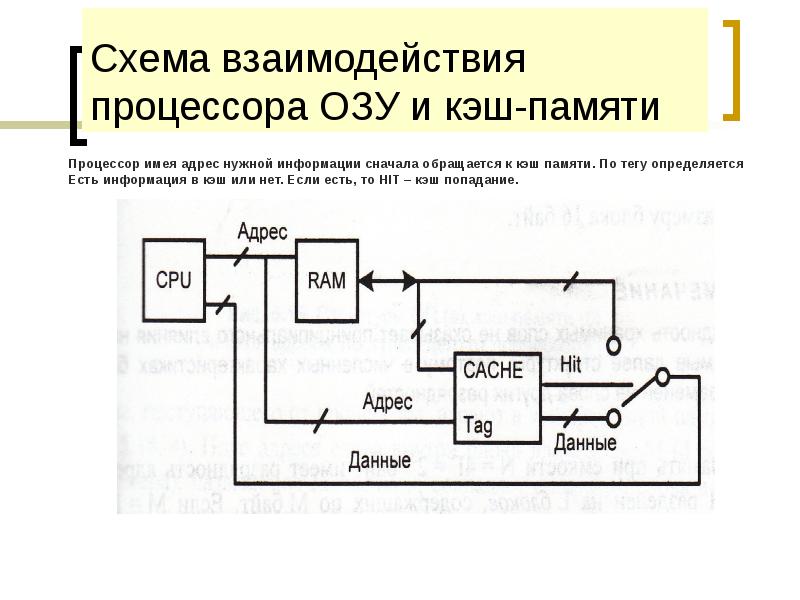

- 19. Схема взаимодействия процессора ОЗУ и кэш-памяти

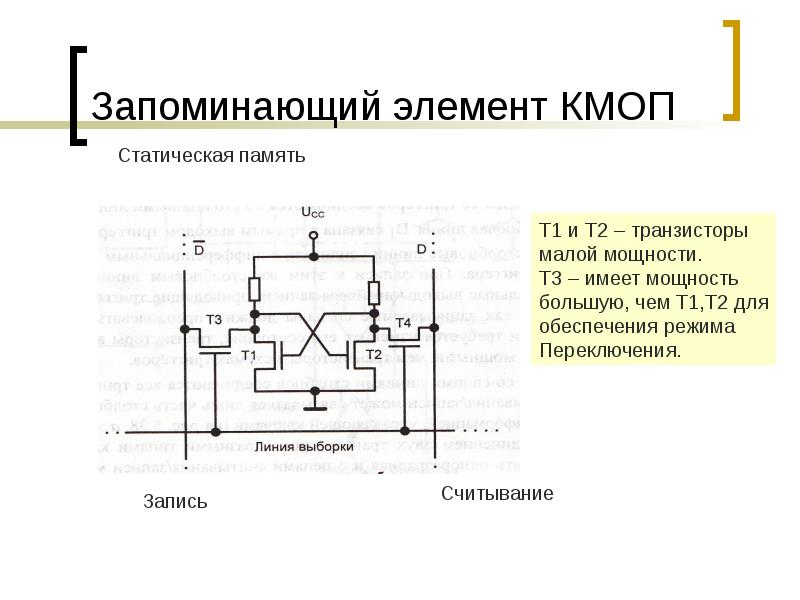

- 20. Запоминающий элемент КМОП

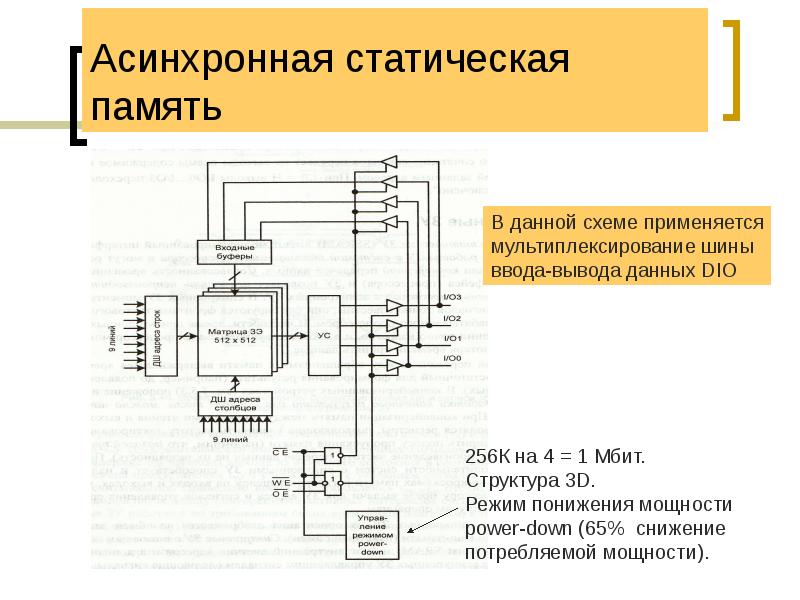

- 21. Асинхронная статическая память

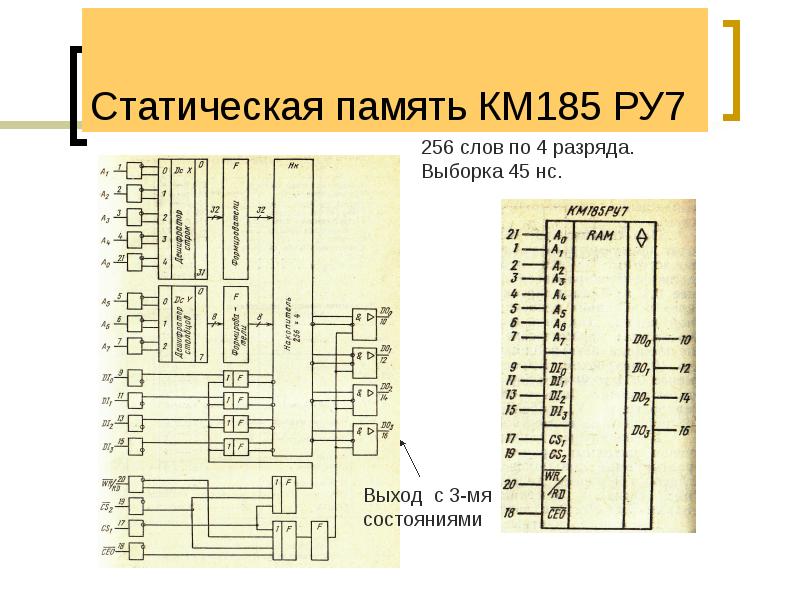

- 22. Статическая память КМ185 РУ7

- 23. Статическая память КМ185 РУ7

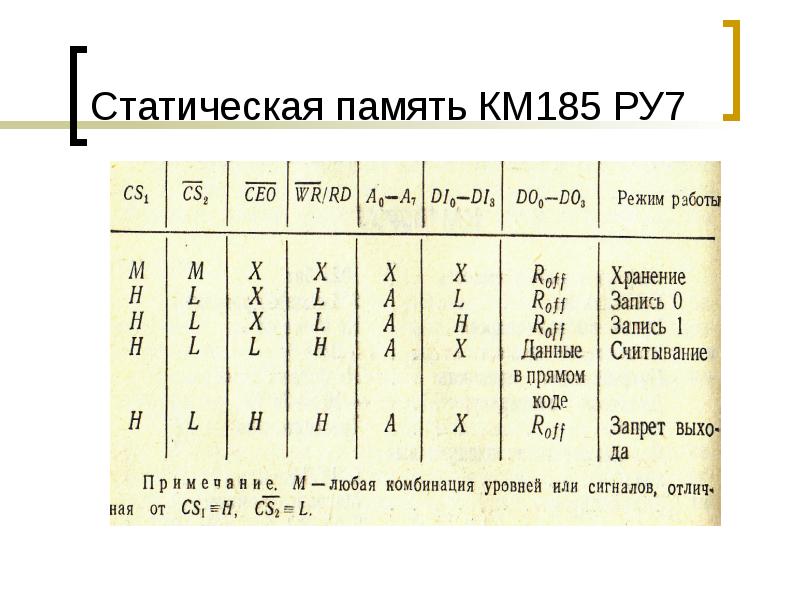

- 24. Статическая память КМ185 РУ7

- 25. Синхронная статическая память

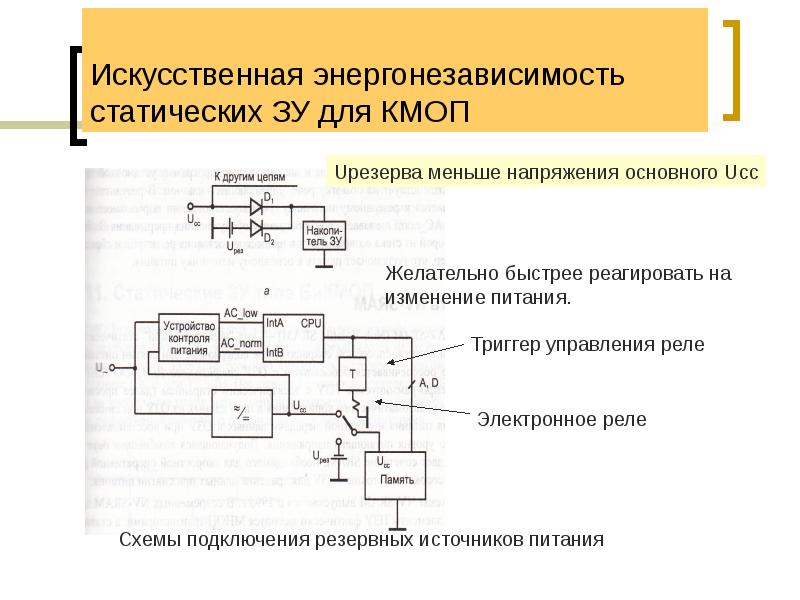

- 26. Искусственная энергонезависимость статических ЗУ для КМОП

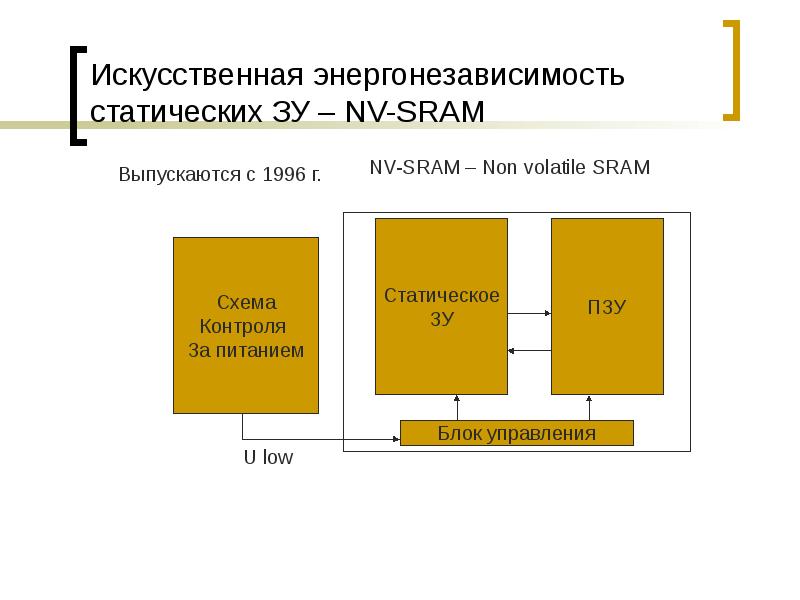

- 27. Искусственная энергонезависимость статических ЗУ – NV-SRAM

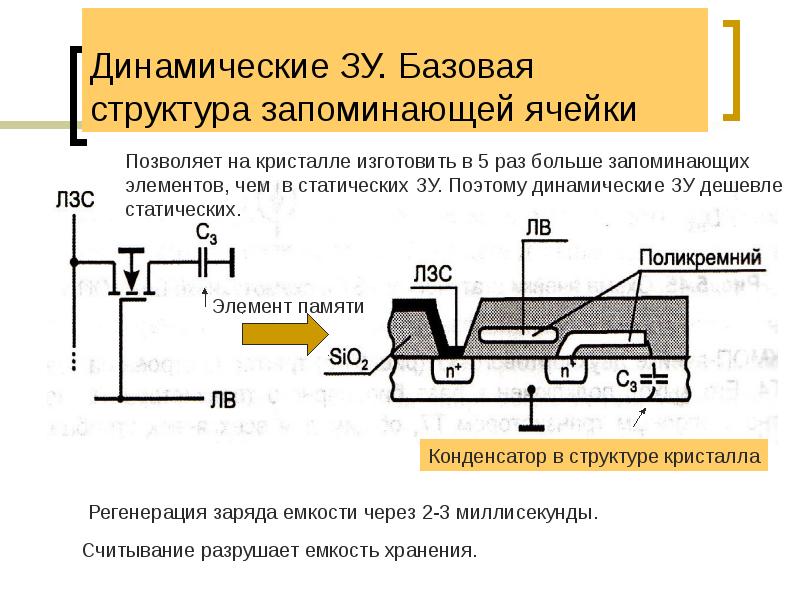

- 28. Динамические ЗУ. Базовая структура запоминающей ячейки

- 29. Особенности динамических ЗУ Поток обращений к динамическому ЗУ должен учитывать состояние

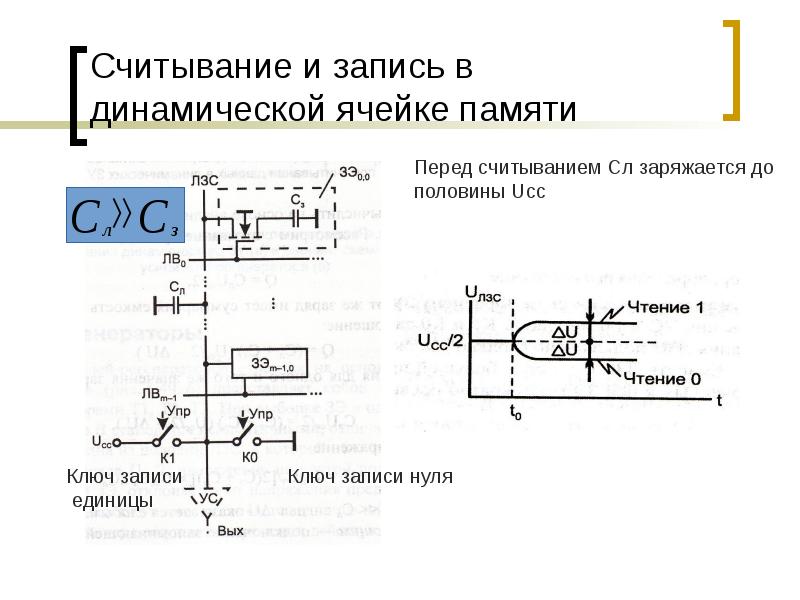

- 30. Считывание и запись в динамической ячейке памяти

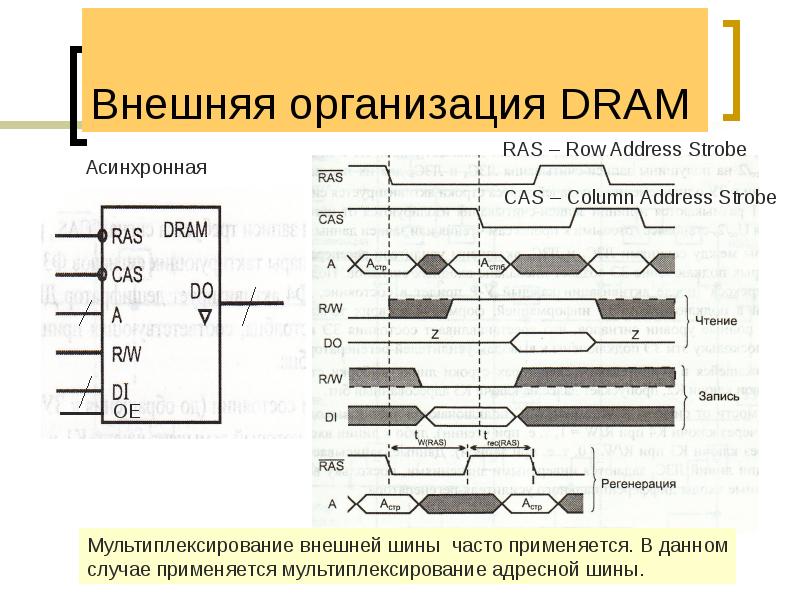

- 31. Внешняя организация DRAM

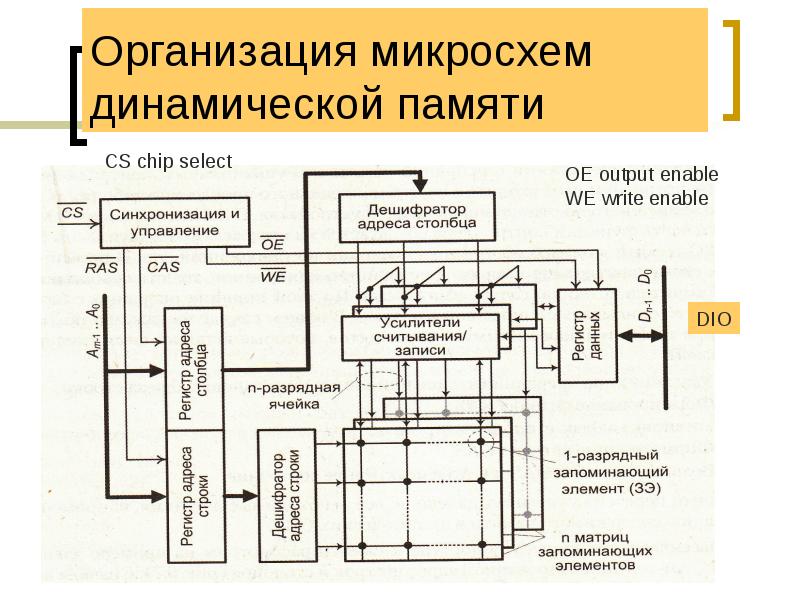

- 32. Организация микросхем динамической памяти

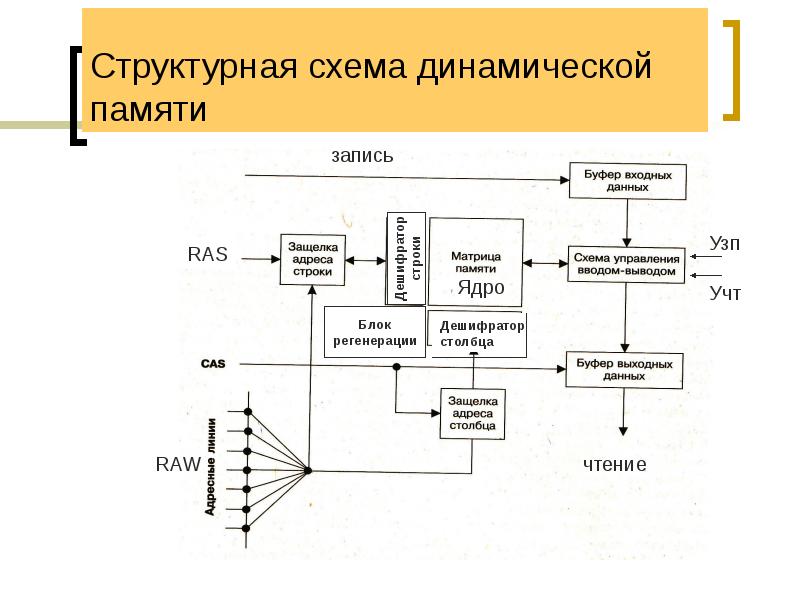

- 33. Структурная схема динамической памяти

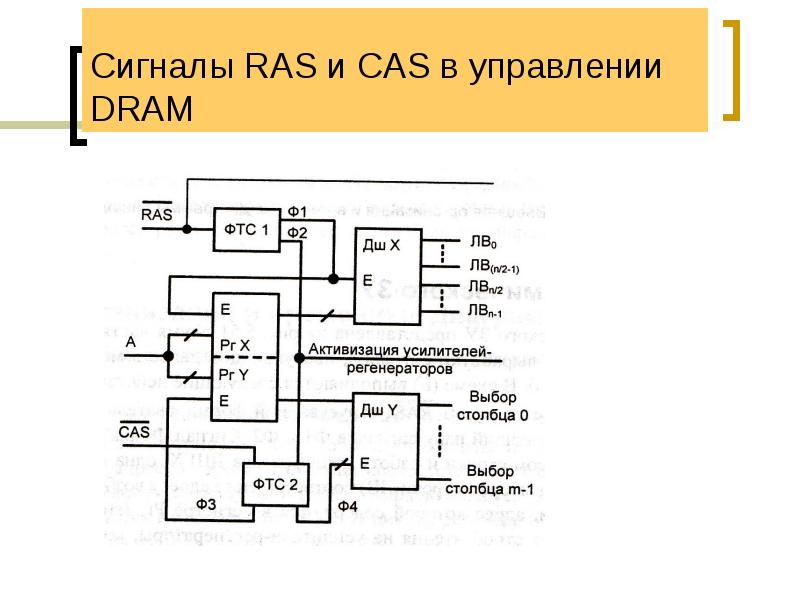

- 34. Сигналы RAS и CAS в управлении DRAM

- 35. Методы повышения быстродействия динамических ЗУ Быстрый страничный доступ. Используется принцип локальности

- 36. Эволюция оперативной памяти динамического типа FPM – Fast Page Mode –

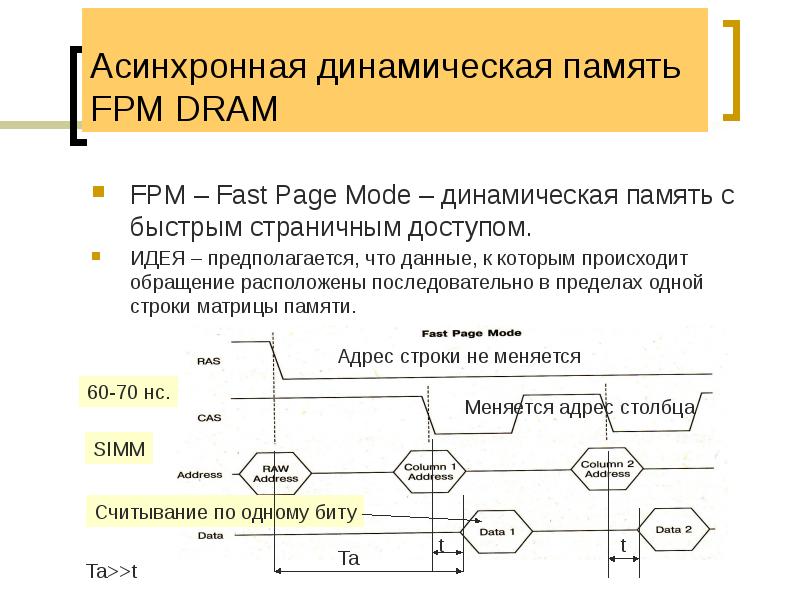

- 37. Асинхронная динамическая память FPM DRAM FPM – Fast Page Mode –

- 38. Асинхронная динамическая память EDO DRAM EDO – Extended Data Out. Расширенное

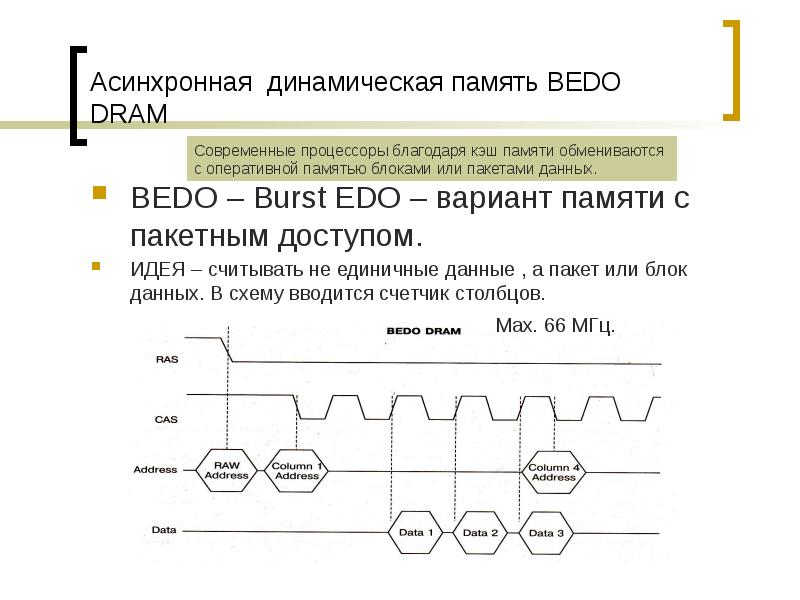

- 39. Асинхронная динамическая память BEDO DRAM BEDO – Burst EDO – вариант

- 40. Недостаток асинхронной динамической памяти Процессор ждет выполнение операций с памятью. Других

- 41. Переход к синхронной динамической памяти. Особенности организации. Увязка операций с тактирующими

- 42. Синхронная динамическая память SDRAM Синхронизация входных и выходных сигналов с тактами

- 43. Синхронная динамическая память SDRAM

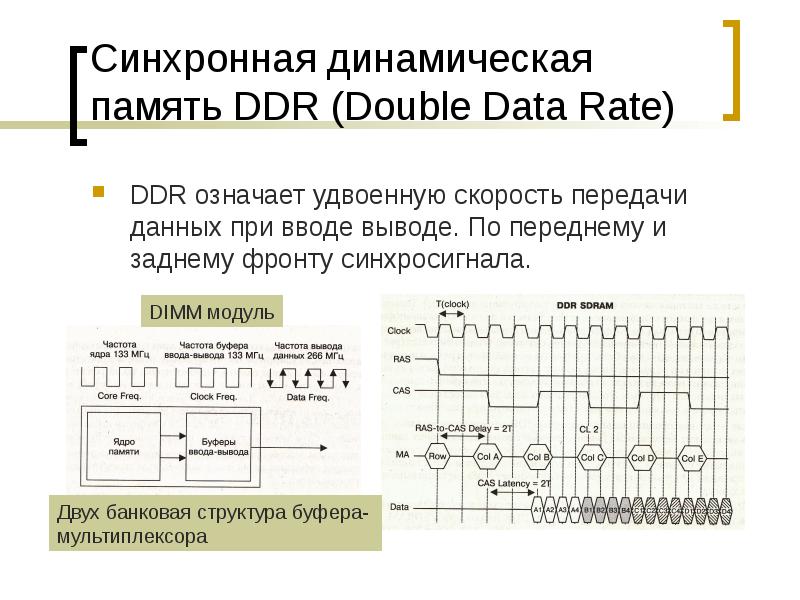

- 44. Синхронная динамическая память DDR (Double Data Rate) DDR означает удвоенную скорость

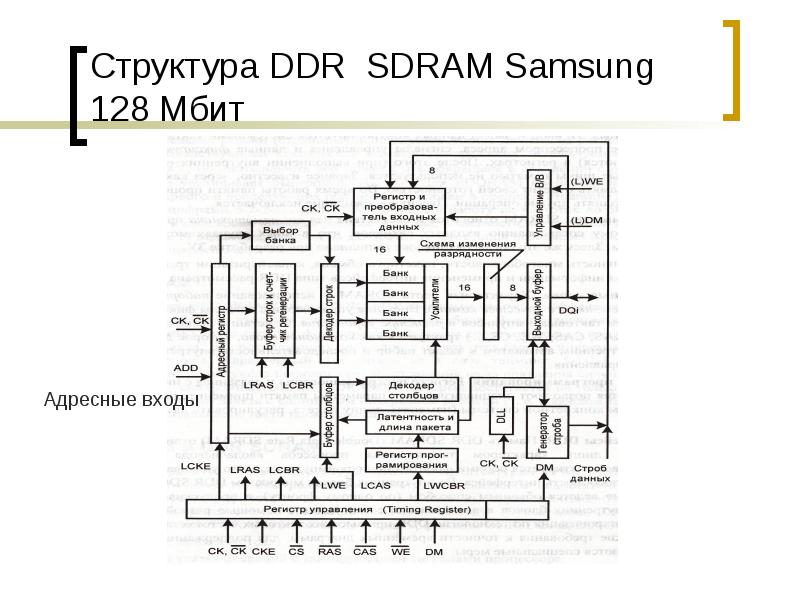

- 45. Структура DDR SDRAM Samsung 128 Мбит

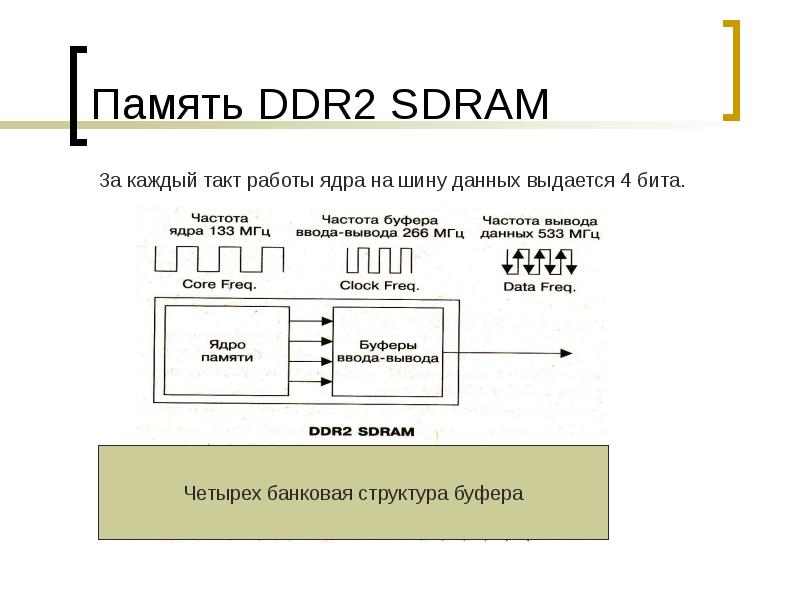

- 46. Память DDR2 SDRAM

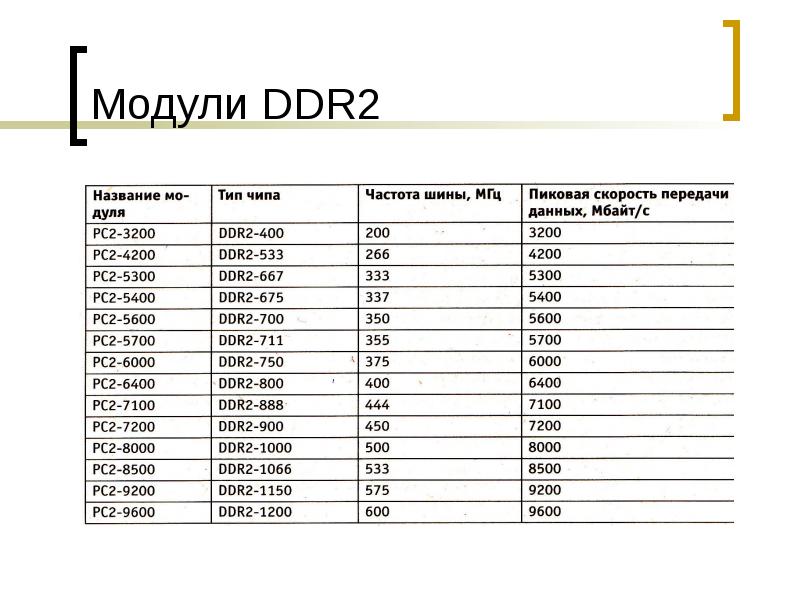

- 47. Модули DDR2

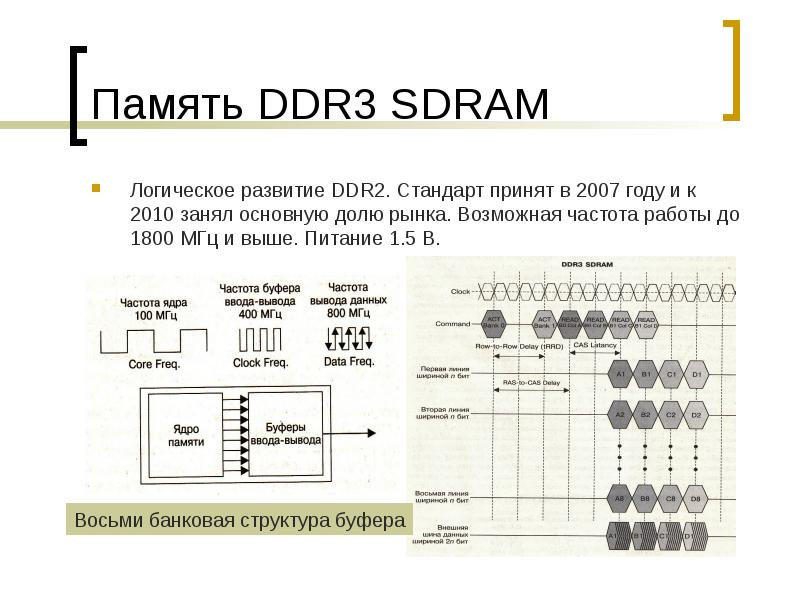

- 48. Память DDR3 SDRAM Логическое развитие DDR2. Стандарт принят в 2007 году

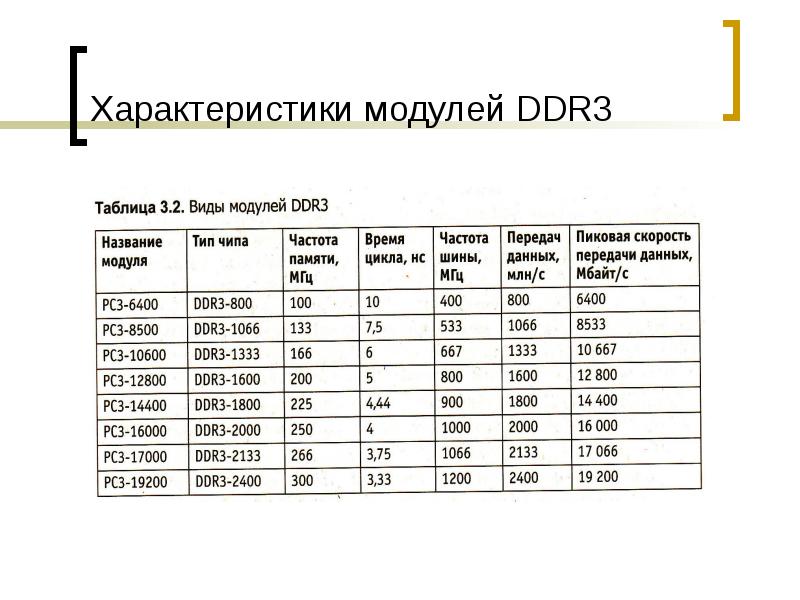

- 49. Характеристики модулей DDR3

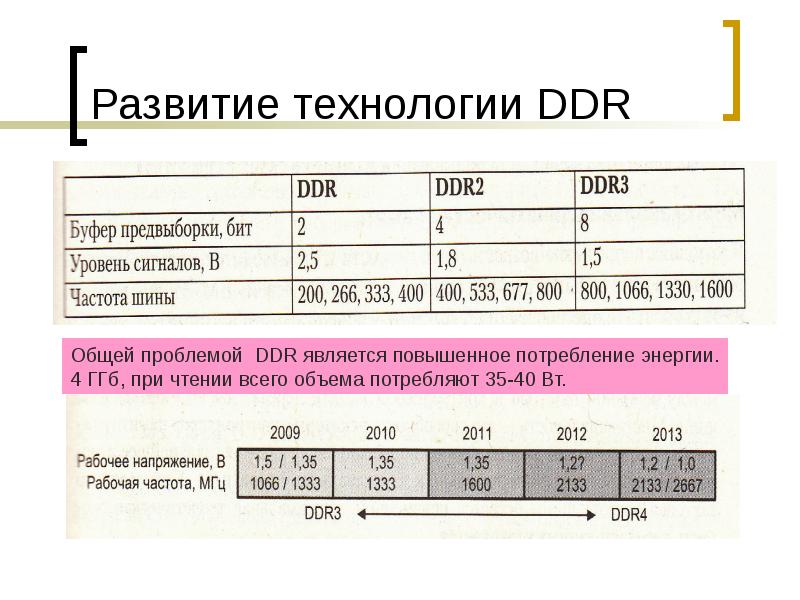

- 50. Развитие технологии DDR

- 51. Rambus DRAM Применяется в графических и мультимедийных приложениях – там где

- 52. RLDRAM (Reduced Latency DRAM) Идея – уменьшение длительности полного цикла обращения

- 53. FCRAM (Fast Cycle RAM) Идея – сегментация ядра памяти и выполнение

- 54. Перспективные ЗУ FRAM – ферроэлектрические. PFRAM – полимерно-ферроэлектрические. MRAM – магниторезистивные.

- 55. Виды модулей оперативной памяти SIMM – (Single In-line Memory Module) -

- 56. Виды модулей оперативной памяти DIMM (Dual In-line Memory Module) – печатная

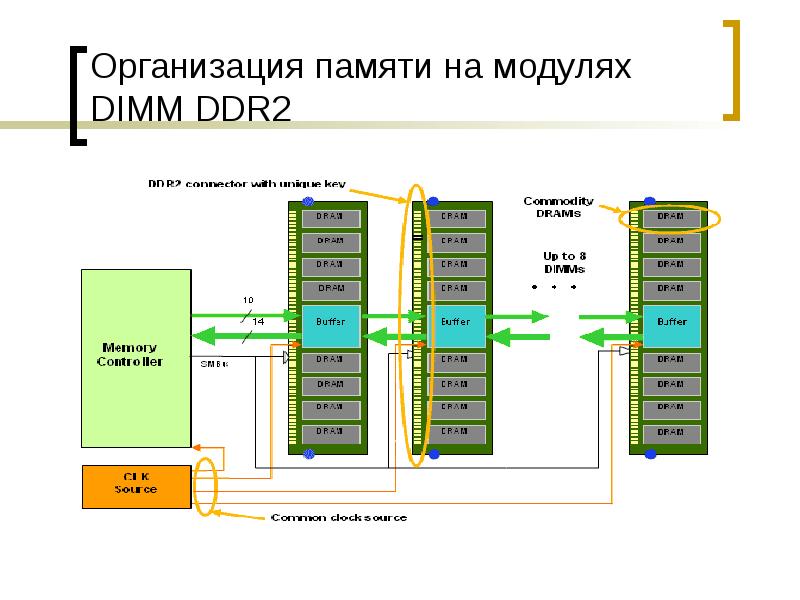

- 57. Организация памяти на модулях DIMM DDR2

- 58. Виды модулей оперативной памяти RIMM (Rambus In-line Memory Module) – похожи

- 59. Энергонезависимые ОЗУ Микросхемы BBSRAM (Battery-Back SRAM) – обычные ОЗУ со встроенным

- 60. Скачать презентацию

Слайды и текст этой презентации

Похожие презентации