Триггеры и сумматоры

Содержание

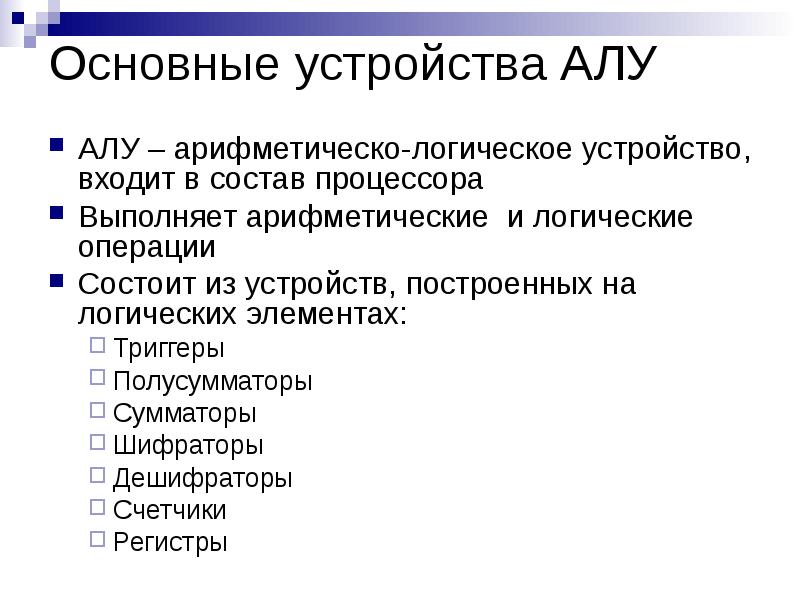

- 2. Основные устройства АЛУ АЛУ – арифметическо-логическое устройство, входит в состав процессора

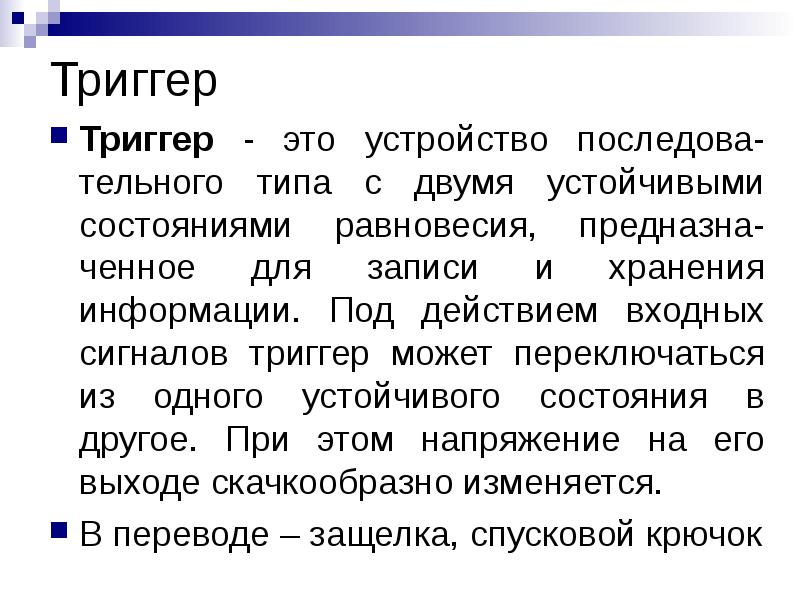

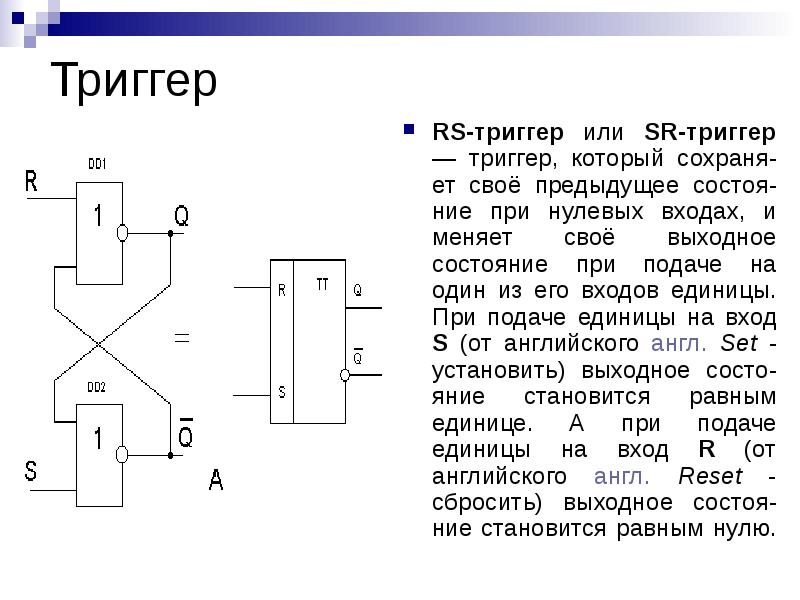

- 3. Триггер Триггер - это устройство последова-тельного типа с двумя устойчивыми состояниями

- 4. Триггер RS-триггер или SR-триггер — триггер, который сохраня-ет своё предыдущее состоя-ние

- 5. Триггер Один триггер хранит бит информации. Для хранения 1 байта

- 6. Регистр Несколько триггеров можно объединить в регистр – устройство для хранения

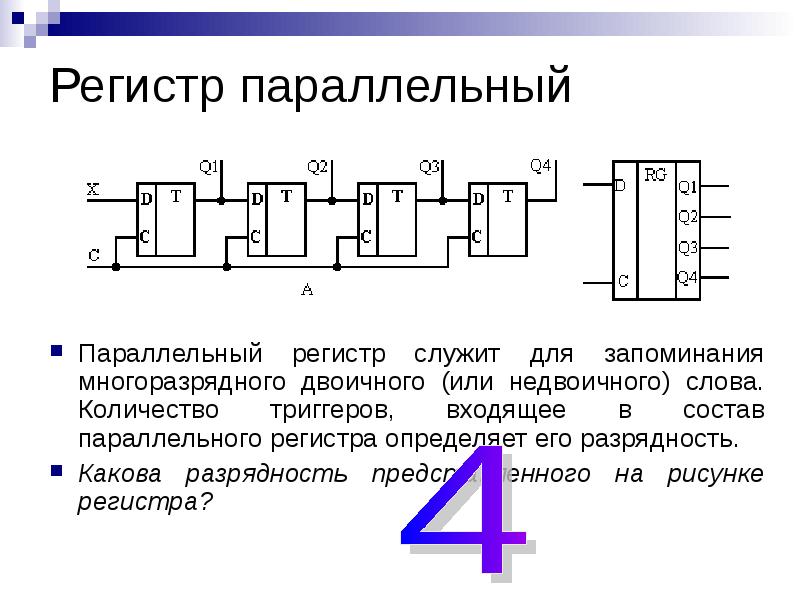

- 7. Регистр параллельный Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного)

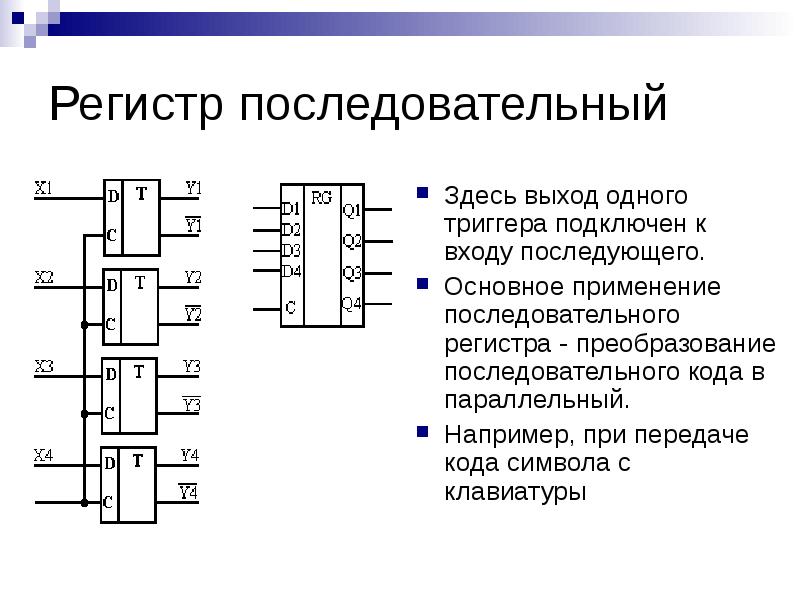

- 8. Регистр последовательный Здесь выход одного триггера подключен к входу последующего.

- 9. Типы регистров Сумматор – регистр АЛУ, способный производить сложение, участвует в

- 10. Сумматор Сумматор является центральным узлом арифметическо-логического устройства компьютера Сумматор выполняет сложение

- 11. Сумматор По числу входов и выходов одноразрядных двоичных сумматоров различают: полусумматоры,

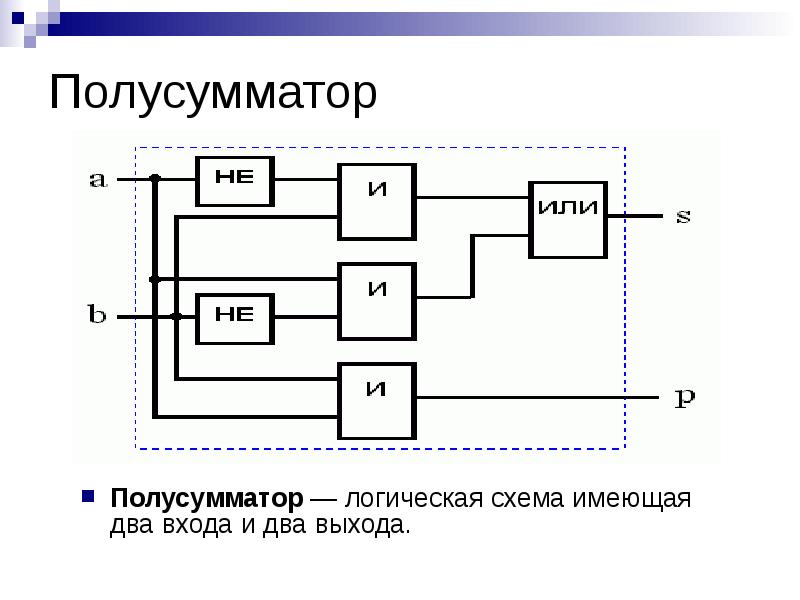

- 12. Полусумматор Полусумматор — логическая схема имеющая два входа и два выхода.

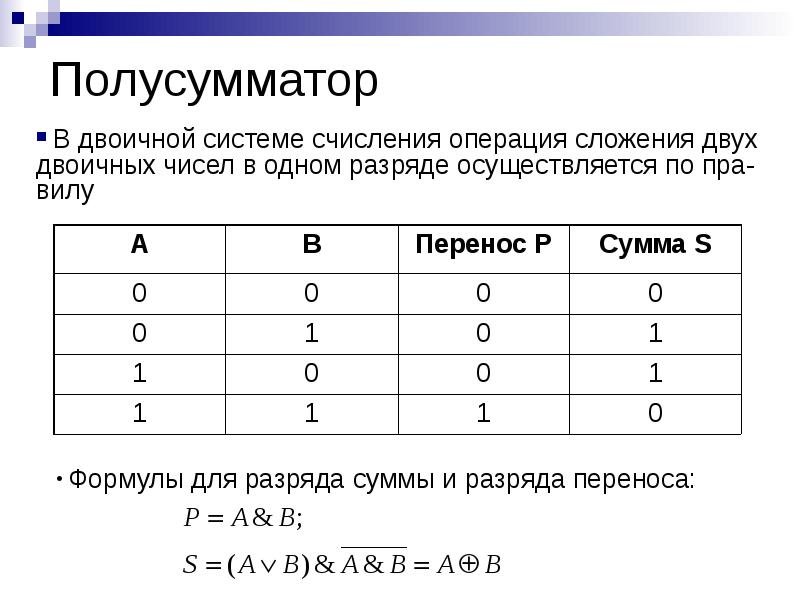

- 13. Полусумматор

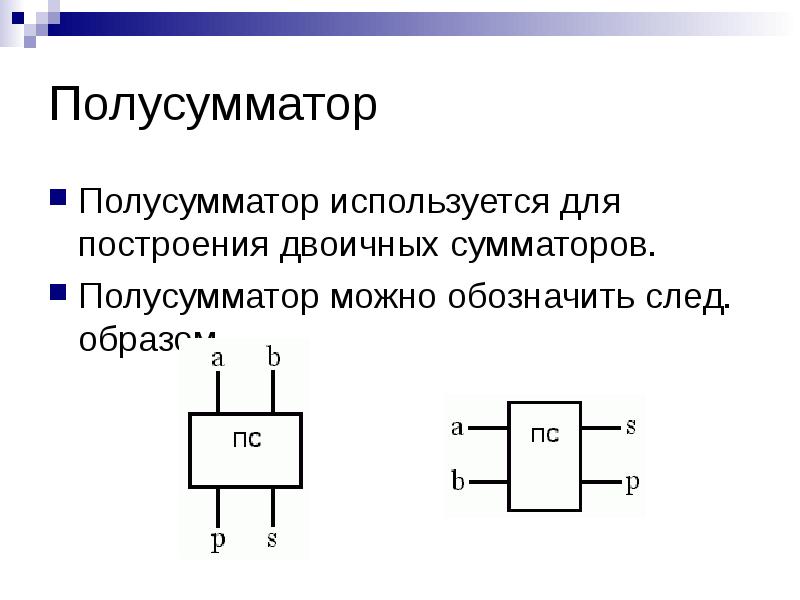

- 14. Полусумматор Полусумматор используется для построения двоичных сумматоров. Полусумматор можно обозначить

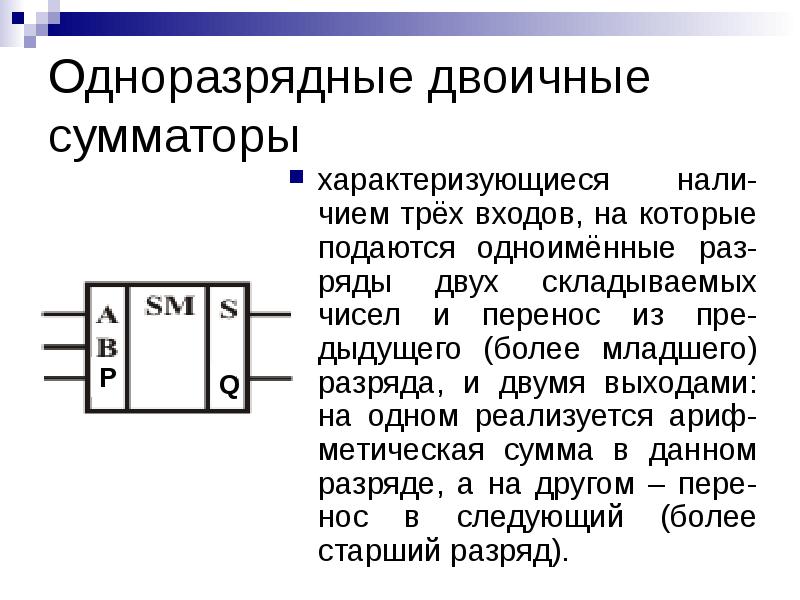

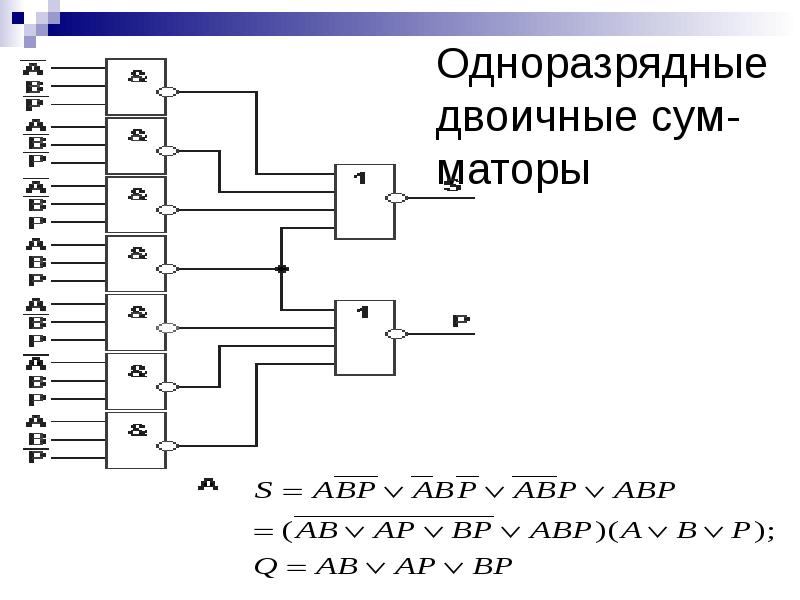

- 15. Одноразрядные двоичные сумматоры характеризующиеся нали-чием трёх входов, на которые подаются одноимённые

- 16. Одноразрядные двоичные сумматоры

- 17. Одноразрядные двоичные сум-маторы

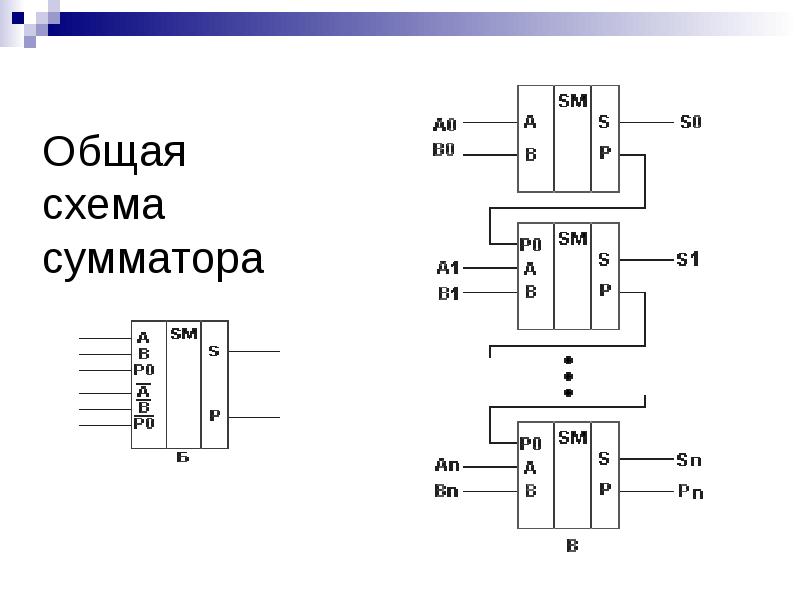

- 18. Общая схема сумматора

- 19. Скачать презентацию

Слайды и текст этой презентации

Похожие презентации