Элементы оборудования информационно-вычислительных комплексов. Системные шины. (Лекция 3а) презентация

Содержание

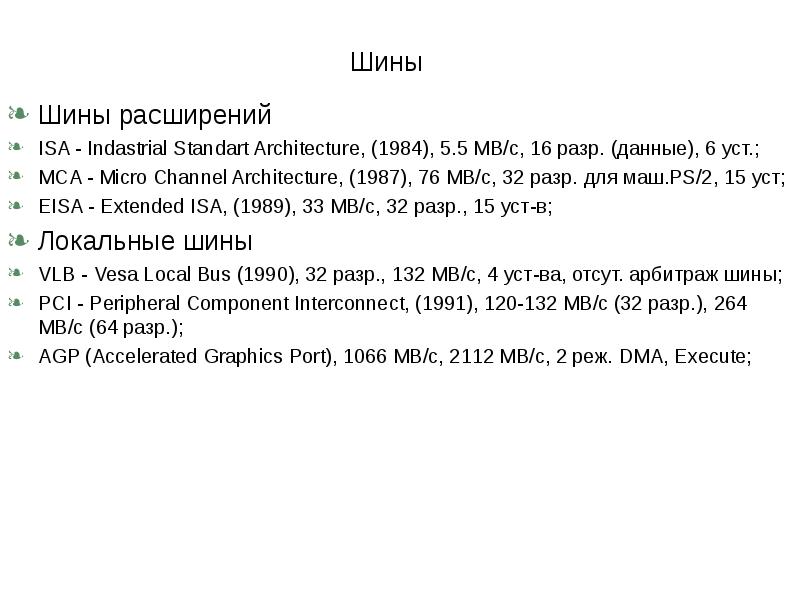

- 2. Шины Шины расширений ISA - Indastrial Standart Architecture, (1984), 5.5 MB/c,

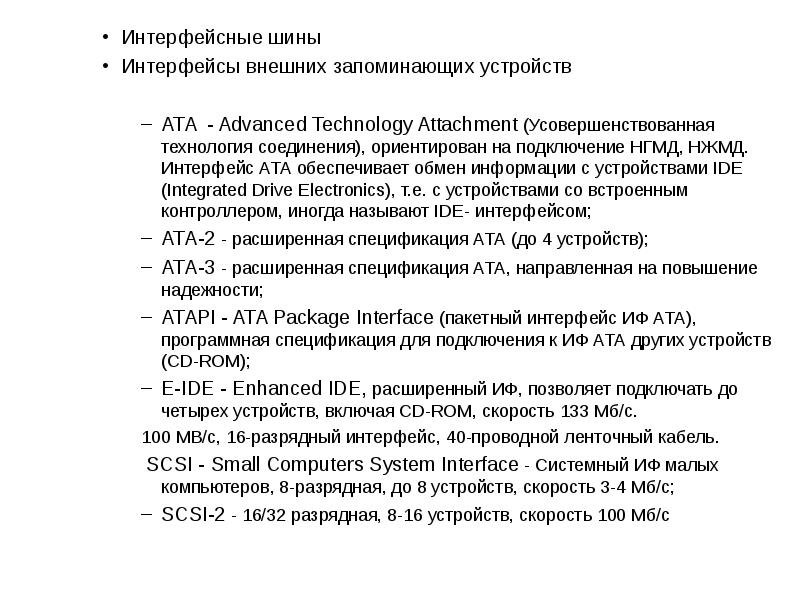

- 3. Интерфейсные шины Интерфейсные шины Интерфейсы внешних запоминающих устройств ATA

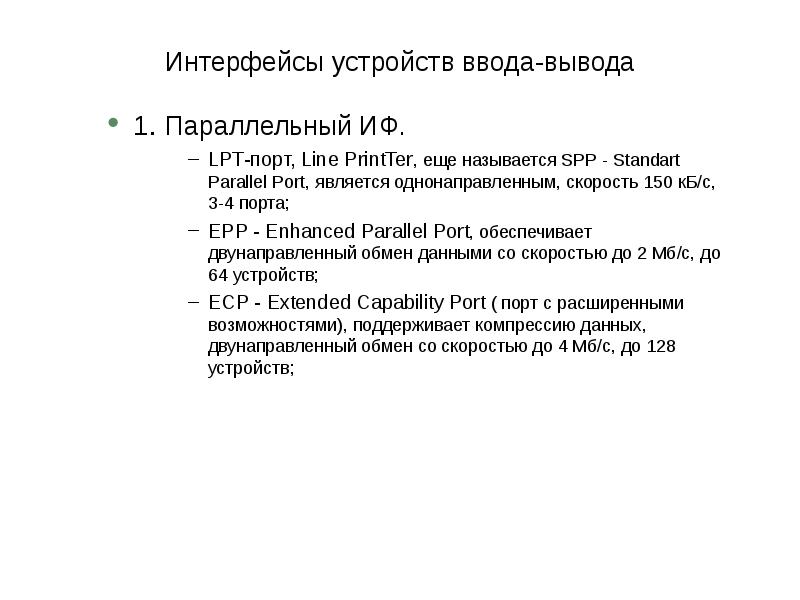

- 4. Интерфейсы устройств ввода-вывода 1. Параллельный ИФ. LPT-порт, Line PrintTer, еще

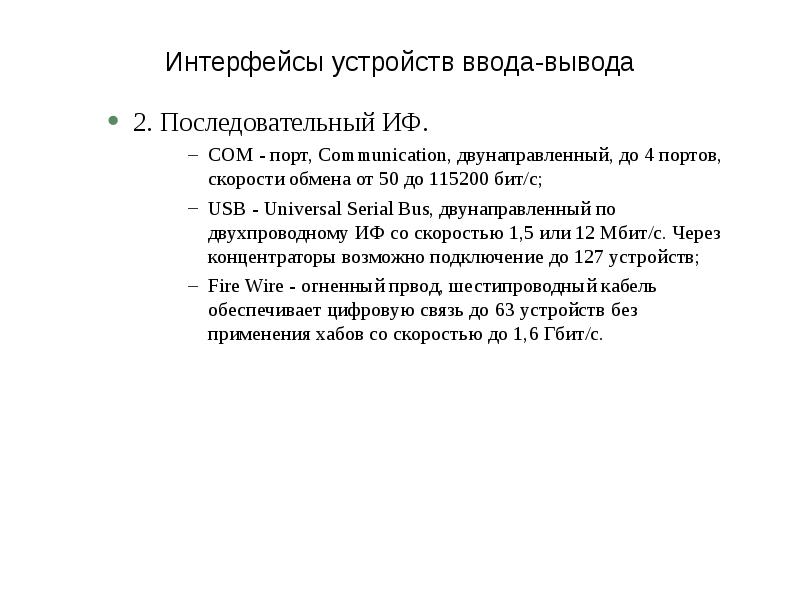

- 5. Интерфейсы устройств ввода-вывода 2. Последовательный ИФ. COM - порт, Communication, двунаправленный,

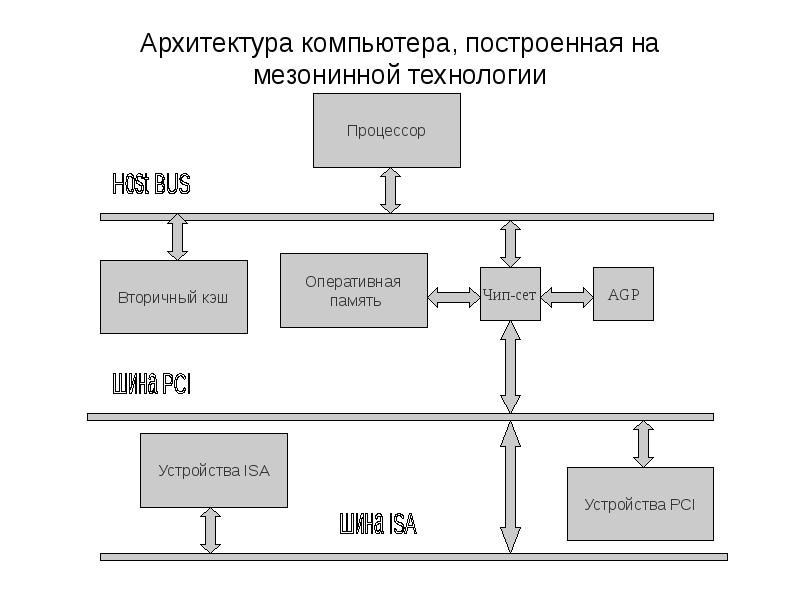

- 6. Архитектура компьютера, построенная на мезонинной технологии

- 7. Системная микросхема (чипсет) 2 базовые микросхемы: северный и южный мост. Северный

- 8. 2.1.2. Специализированные системные шины. Особенности промышленных компьютеров. VME - bus, поддерживает

- 9. 2.2. Архитектура современных процессоров Двумя основными архитектурами набора команд, используемыми компьютерной

- 10. Основоположником CISC-архитектуры можно считать компанию IBM с ее базовой архитектурой /360,

- 11. Основой архитектуры современных рабочих станций и серверов является архитектура компьютера с

- 12. В 1980 году Д.Паттерсон со своими коллегами из Беркли начали свой

- 13. Эти три машины имели много общего. Все они придерживались архитектуры, отделяющей

- 14. Отметим, что разработках компании Intel (имеется в виду Pentium P54C и

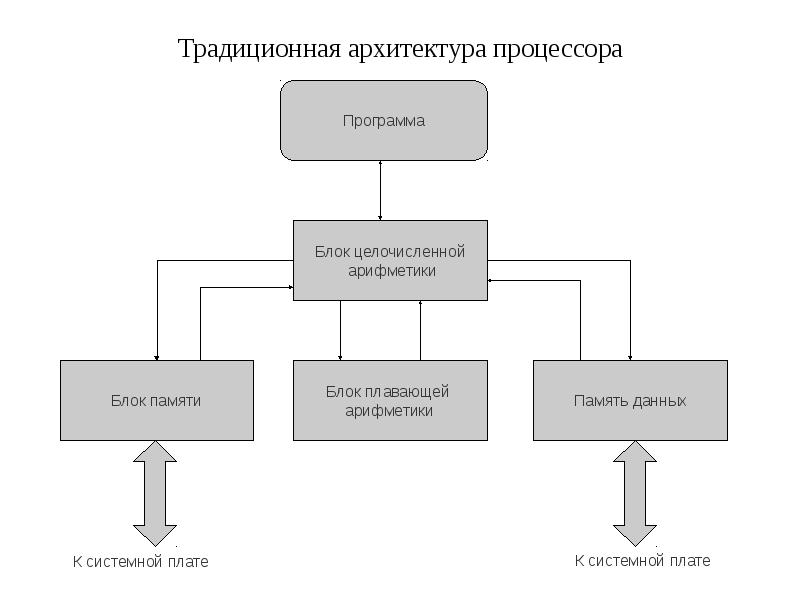

- 15. Традиционная архитектура процессора

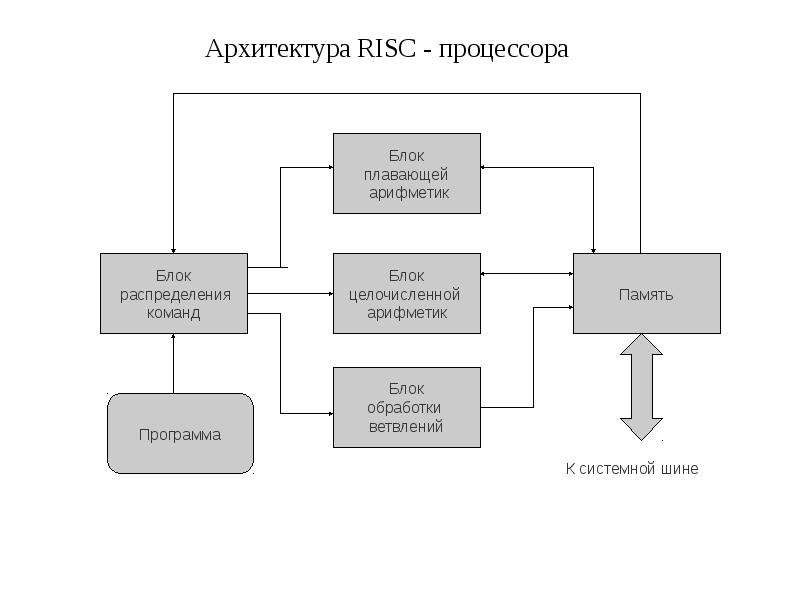

- 16. Архитектура RISC - процессора

- 17. Cуперскалярные и суперконвейерные процессоры. Примеры реализации. Суперконвейерный подход: каждая команда

- 18. Суперскалярный подход, используется : конвейерная обработка команд, но значительно короче; распараллеливание

- 19. Скачать презентацию

Слайды и текст этой презентации

Скачать презентацию на тему Элементы оборудования информационно-вычислительных комплексов. Системные шины. (Лекция 3а) можно ниже:

Похожие презентации