Шина LPC презентация

Содержание

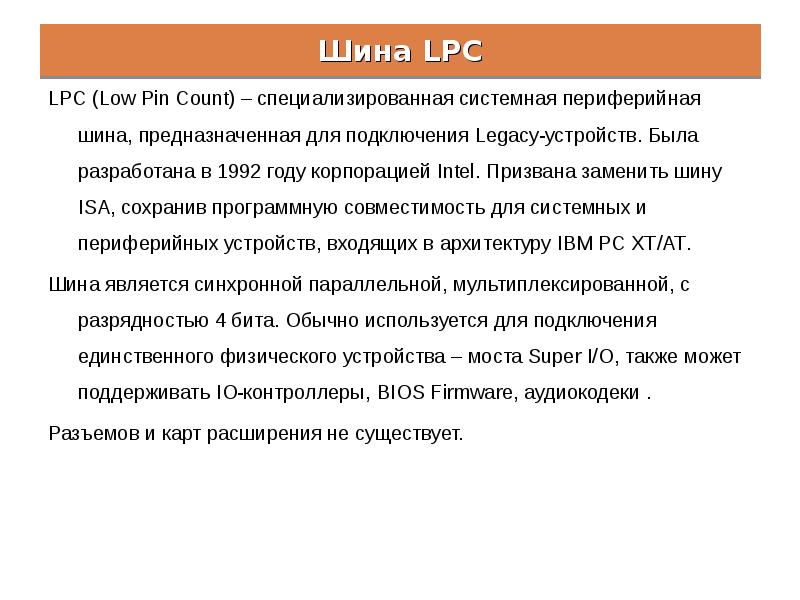

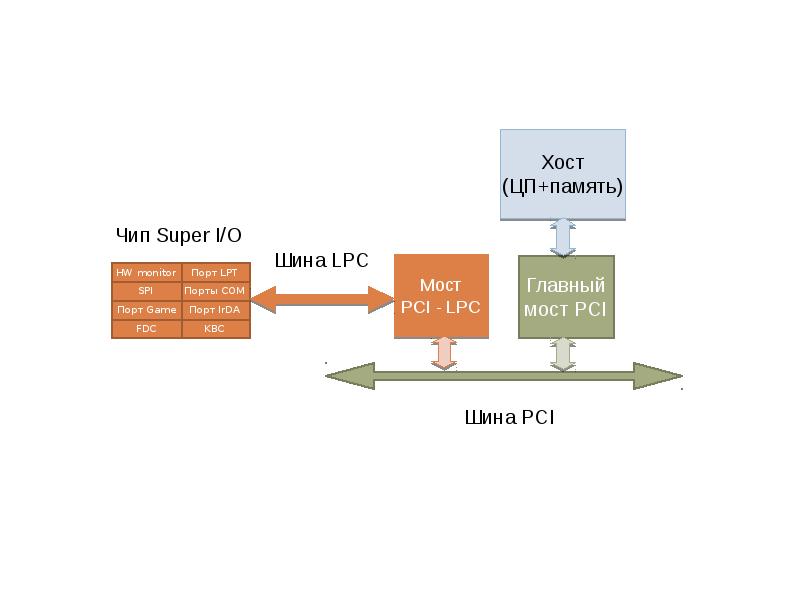

- 2. Шина LPC LPC (Low Pin Count) – специализированная системная периферийная шина,

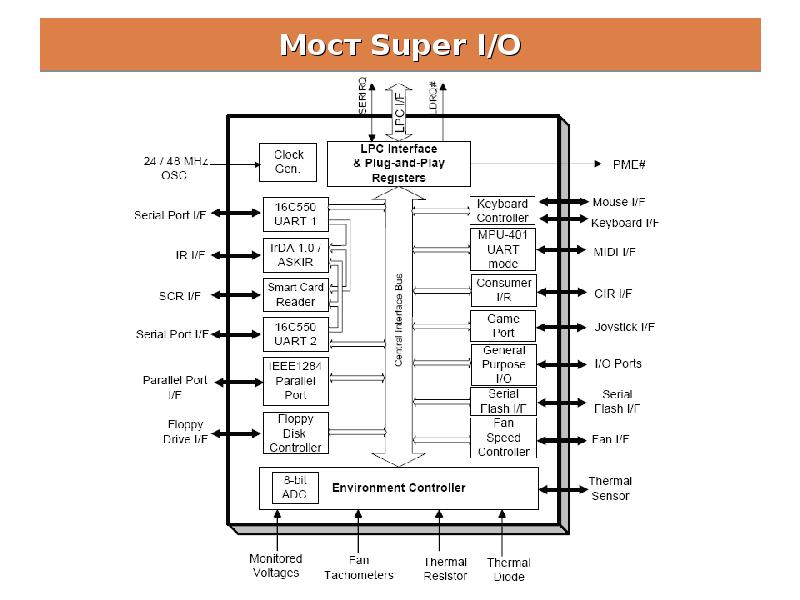

- 4. Мост Super I/O

- 5. Состав моста Super I/O Обязательные компоненты моста Super I/O: Два приемопередатчика

- 6. Состав моста Super I/O Часто мост Super I/O содержит: Дополнительные контакты

- 7. Характеристики LPC Предназначена для подключения чипов на материнской плате. Синхронная, частота

- 8. Сигналы шины LPC Обязательные сигналы: LAD[3:0] – мультиплексированная шина команд, адреса

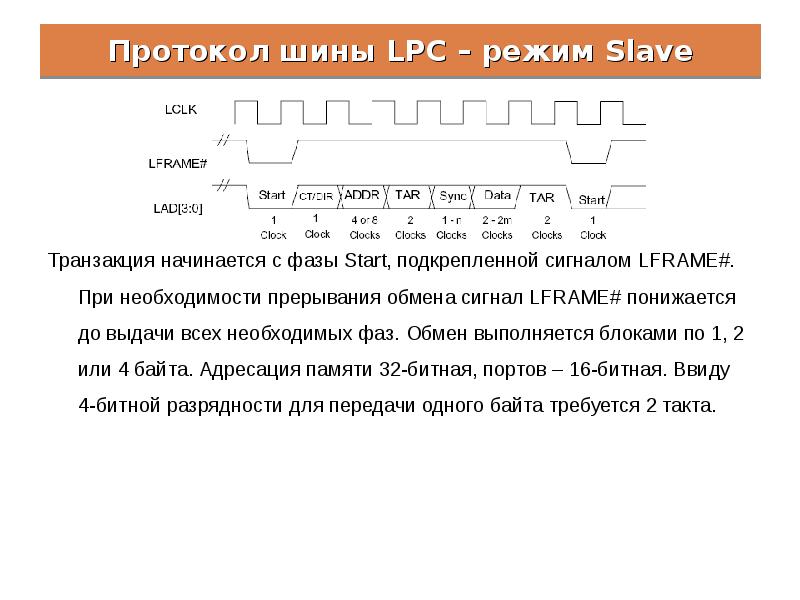

- 9. Протокол шины LPC – режим Slave Транзакция начинается с фазы Start,

- 10. Фазы транзакции LPC Start – начало транзакции: 0000 – начало slave-обмена,

- 11. (продолжение) ADDR – адрес, не используется в операциях DMA: Занимает 4

- 12. Протокол шины LPC – DMA Запрос на открытие канала DMA подает

- 13. (продолжение) Формат транзакции DMA изменен. Вместо фазы ADDR подается фаза Size:

- 14. Протокол шины LPC – Bus Master Предусмотрено управление всего двумя мастерами.

- 15. Скачать презентацию

![Сигналы шины LPC

Обязательные сигналы:

LAD[3:0] – мультиплексированная шина команд, адреса Сигналы шины LPC

Обязательные сигналы:

LAD[3:0] – мультиплексированная шина команд, адреса](/documents_3/f9465b5d21ff351874cdf8a0bd9822fa/img7.jpg)

Слайды и текст этой презентации

Похожие презентации