Организация ЭВМ и систем. Основные характеристики системы памяти. Кэш-память. (Лекция 10) презентация

Содержание

- 2. Организация интерфейса памяти Появления 32-разрядного МП определило использование 3 новых концепций

- 3. Иерархия подсистемы памяти ПК Регистровая память (сверхоперативное запоминающее устройство). Буферная память

- 4. Кэш-память Кэш-память представляет собой быстродействующее ЗУ, размещенное на одном кристалле с

- 5. Для согласования содержимого кэш-памяти и ОП используют 3 метода записи:

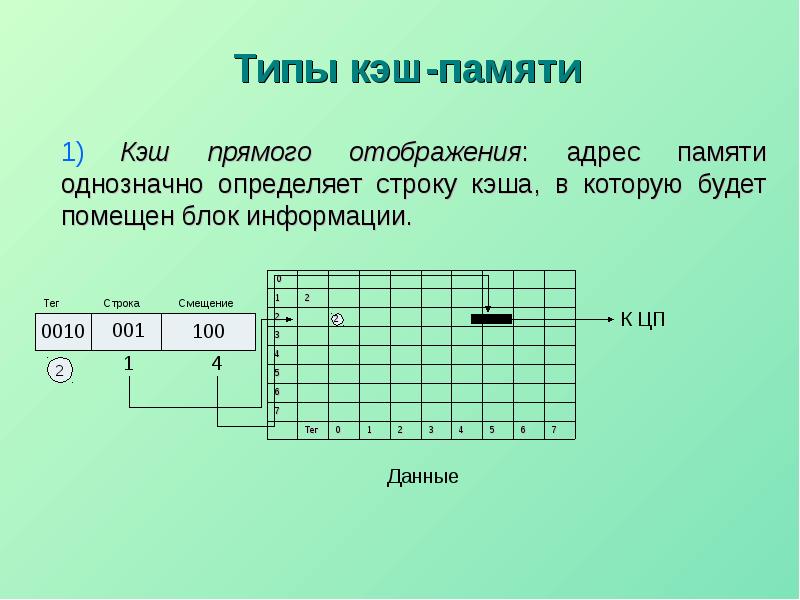

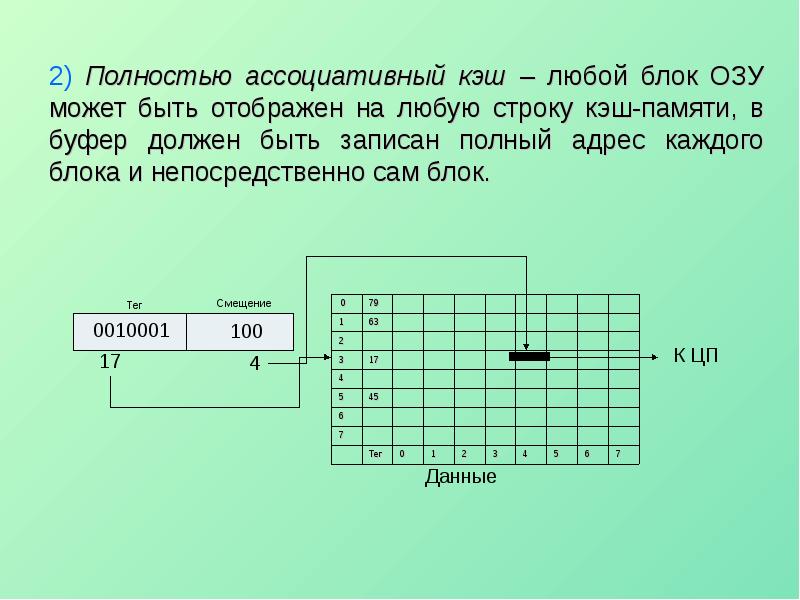

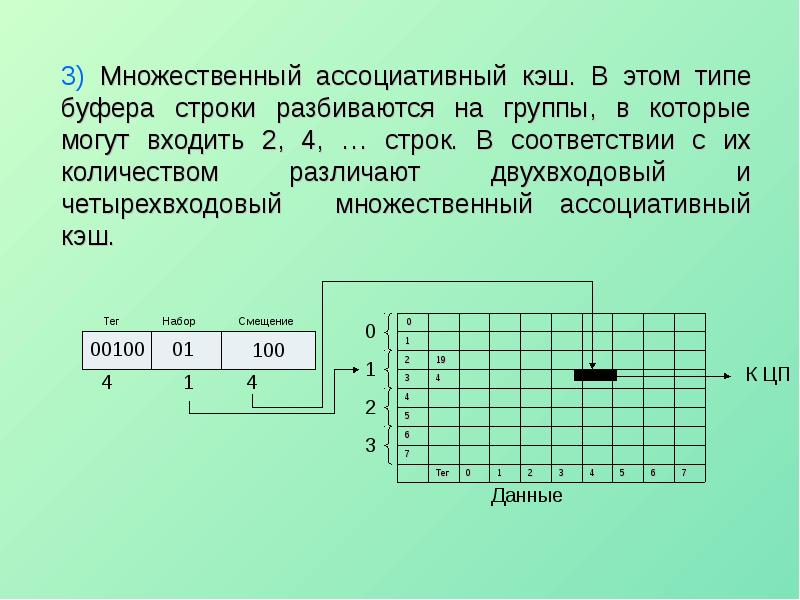

- 6. Типы кэш-памяти

- 9. Типы кэш-памяти Кэш Гарвардской архитектуры – раздельные кэш-команд и кэш-данных. Кэш

- 10. Размер и эффективность кэш-памяти

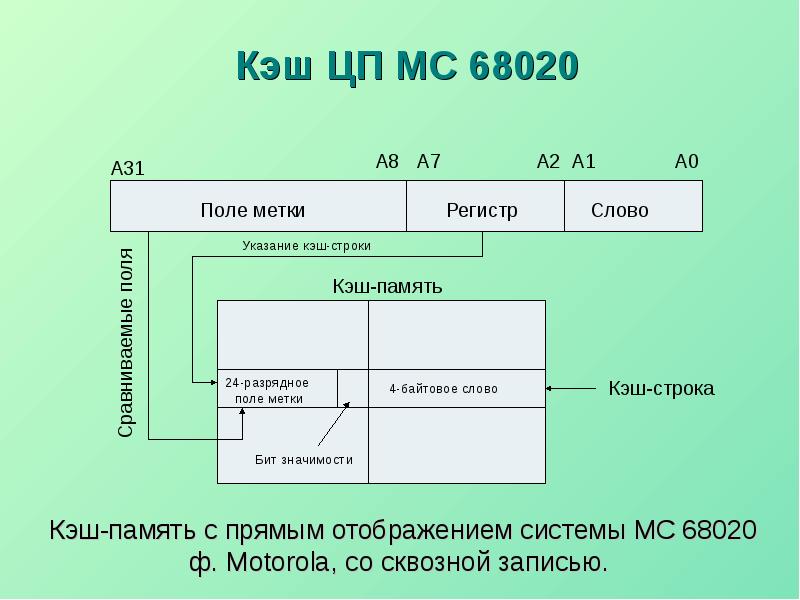

- 11. Кэш ЦП МС 68020

- 12. Новые технологии памяти Для повышения быстродействия DRAM используются 2 основных

- 13. Новые технологи памяти CDRAM (Cache DRAM) EDRAM (Enhanced DRAM )

- 14. FPM DRAM Идет последовательное обращение к ячейкам одной строки матрицы. При

- 15. EDO DRAM Выходные данные сохраняются в специальном регистре - регистре-защелке. Считывание

- 16. BEDO DRAM Является развитием конвейерной архитектуры. Кроме регистра-защелки появляется

- 17. SDRAM Synchronous (синхронная) DRAM синхронизирована с системным таймером, управляющим

- 20. RDRAM RDRAM - многофункциональный протокол обмена данными между

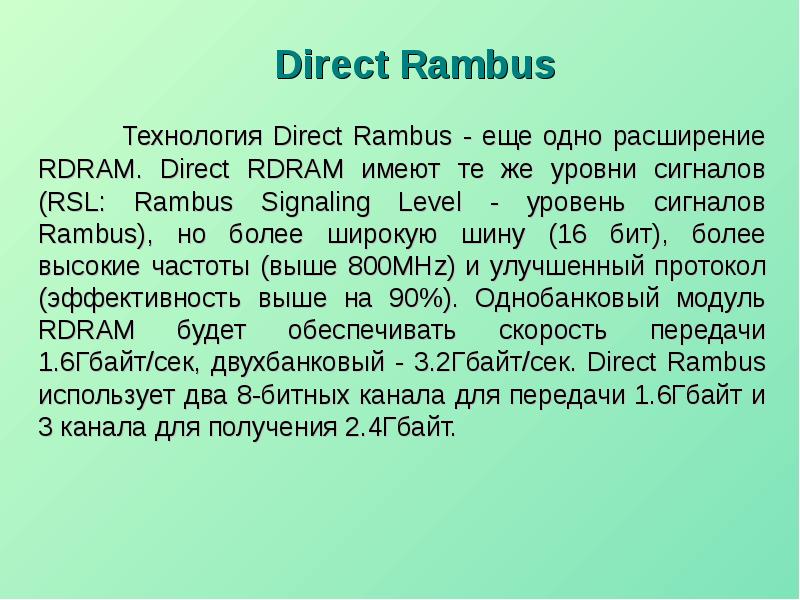

- 22. Direct Rambus Технология Direct Rambus - еще одно расширение

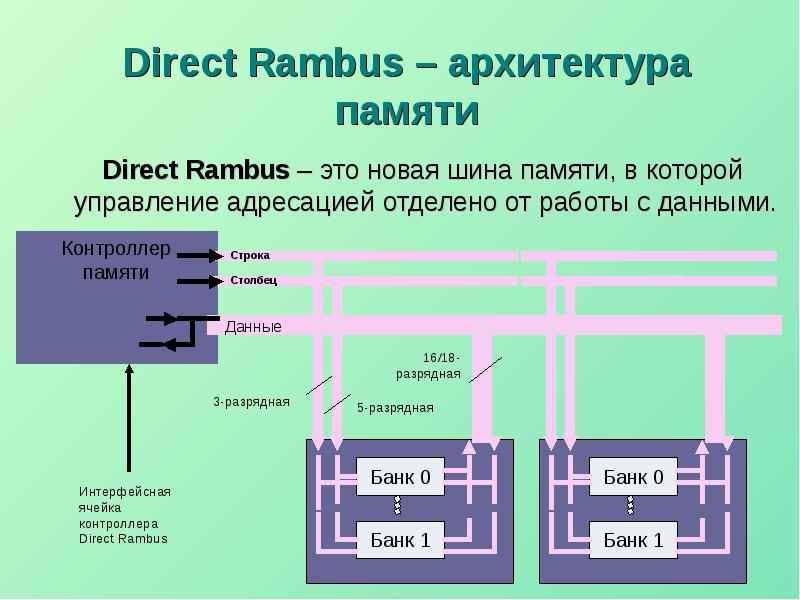

- 23. Direct Rambus – архитектура памяти

- 24. Вопросы для самоконтроля Какая память в ПК является самой быстрой? Объясните,

- 25. Вопросы для самоконтроля В каких микросхемах динамической памяти используется внутренняя конвейерная

- 26. Скачать презентацию

Слайды и текст этой презентации

Скачать презентацию на тему Организация ЭВМ и систем. Основные характеристики системы памяти. Кэш-память. (Лекция 10) можно ниже:

Похожие презентации